# **Frequency Synthesis**

#### Patricia Desgreys **TELECOM201b** Filière TELECOM - 2A

IP Paris – TELECOM Paris COMELEC – LTCI 19, place Marguerite Perey 91120 Palaiseau http://www.comelec.enst.fr/

🛞 IP PARIS

Digital Transceiver RF Front-end

RF oscillators

PLLs

Indirect frequency synthesis

#### **Transceiver chain**

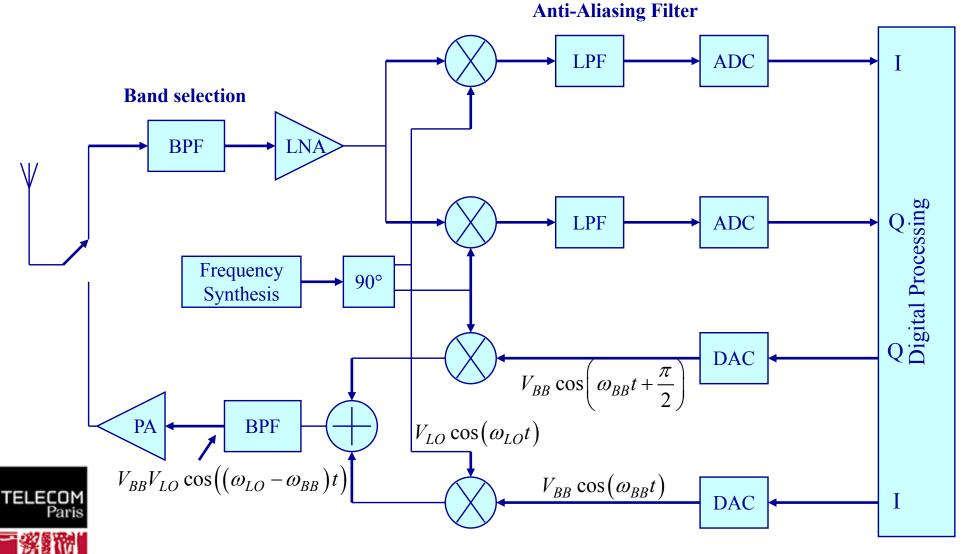

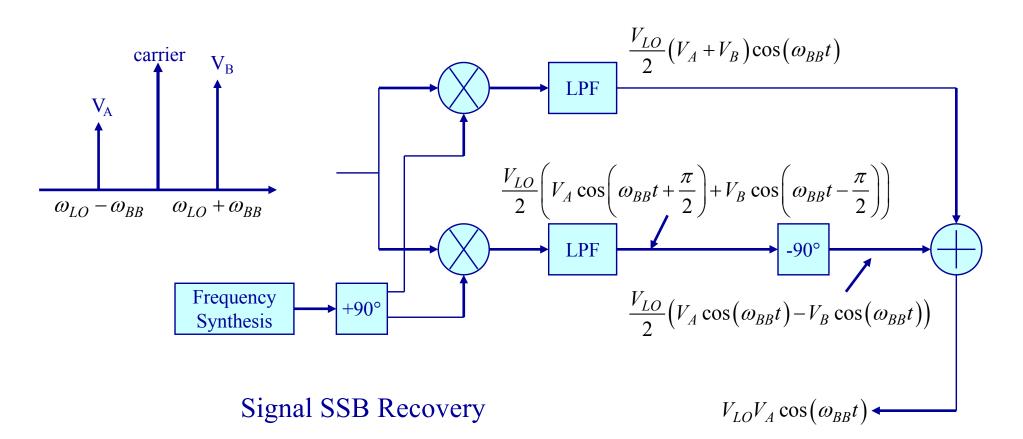

Direct conversion transceiver SSB

😥 IP PARIS

## **Single-Side Band Transceiver**

#### RF frequency synthesis: RF oscillator, PLL

$f_{LO} = f_0 + k f_{ch}$  Chanel selection

Mixer converts signal band around carrier frequency down to DC (baseband)

🛞 IP PARIS

## **Key functions**

Almost all the functions are implemented in digital signals :

- Coding/decoding

- Modulation/demodulation (amplitude, frequency or phase)

- Pulses shaping (raised cosine filtering)

A few analog functions remain unavoidable :

- LNA, Mixers

- Power amplifiers

- Filters

- ADC & DAC

- RF oscillators

- PLLs

- Frequency synthesizers

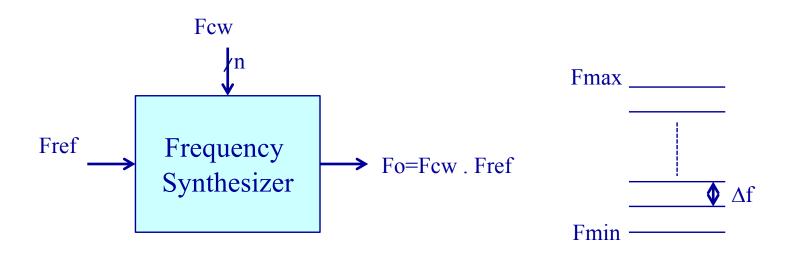

## **Frequency synthesizer**

The "black box" view of a frequency synthesizer is a block getting a very stable reference frequency (usually provided by quartz oscillator) and delivering a set of frequencies between  $F_{min}$  and  $F_{max}$  with a resolution of  $\Delta f$ :

The frequency range  $[F_{min}, F_{max}]$  and the resolution  $\Delta f$  are synthesizer fundamental specifications which depend on the application.

🛞 IP PARIS

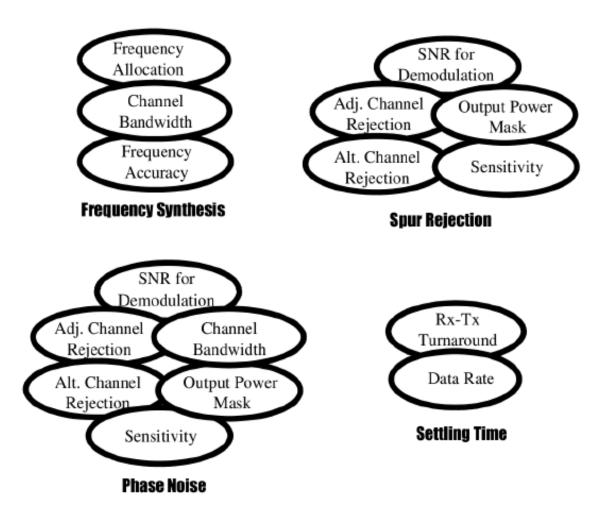

# **Main specifications**

- Frequency range

- Resolution

- Accuracy

- Settling time

- Reference frequency

- Spurs

- Power consumption

- Temperature stability

- Phase noise

🚫 IP PARIS

#### Digital Transceiver RF Font-end

#### PLLs

#### Indirect frequency synthesis

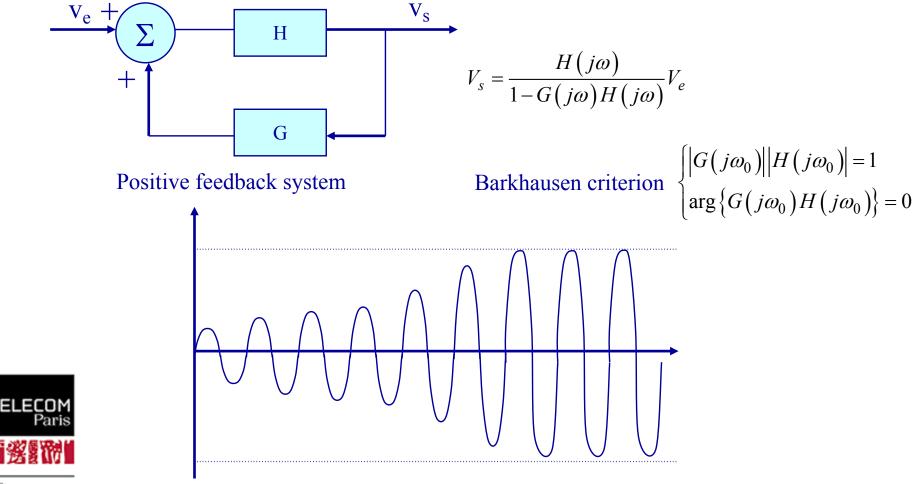

#### **RF oscillators - Introduction**

An oscillator must provide a self-sustaining periodic signal

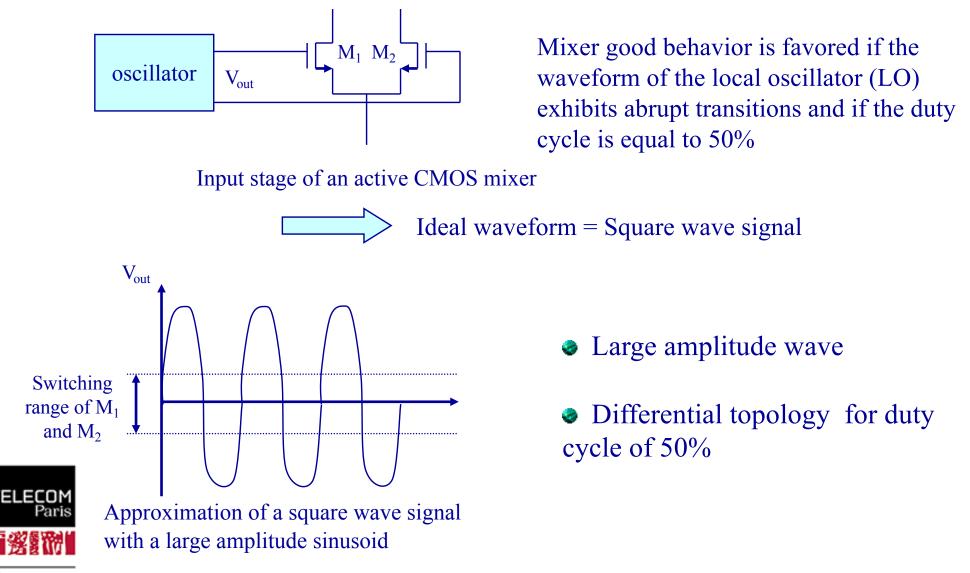

### **RF oscillators – Output waveform**

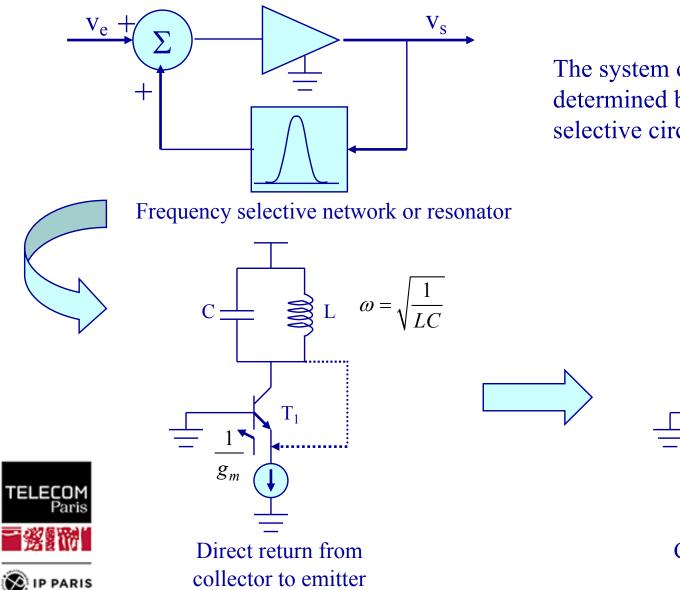

#### **RF oscillators – Frequency selection**

The system oscillations frequency is determined by the characteristics of the selective circuit.

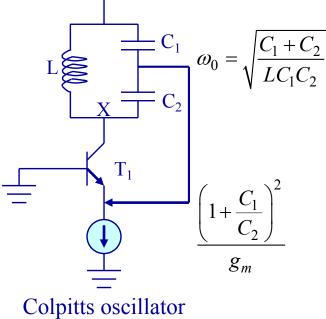

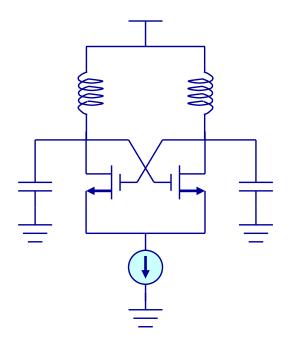

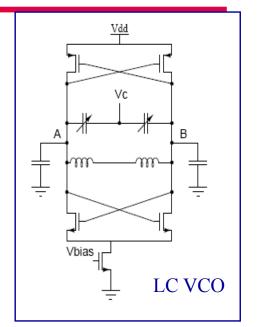

#### **RF oscillators – LC Architecture**

Pros : High quality factor One single inductor

🚫 IP PARIS

Large ratio  $C_1/C_2$ One terminal output

CMOS differential architecture

- Pros : High quality factor Differential output

- Cons : Matching of the two LC cells

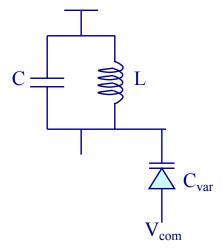

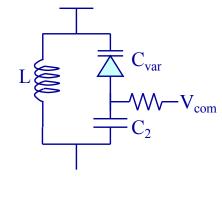

## Voltage Controlled RF oscillators (VCO)

- Need to obtain an adjustable frequency RF oscillation for channel selection :  $f_{LO} = f_0 + k f_{ch}$

- Frequency value controlled by a voltage

$C_{\text{var}} = \frac{C_0}{\left(1 - \frac{V_{com}}{V_{diff}}\right)^2}$

Use of a varicap diode in the LC cell

## **Voltage Controlled RF oscillators (VCO)**

• VCO mathematical model

$$\omega_{LO} = \omega_{FR} + K_{VCO}V_{com} = \frac{d\Phi}{dt}$$

$X(t) = V_{LO}\cos(\Phi) = V_{LO}\cos(\omega_{FR}t + K_{VCO}\int V_{com}dt)$

• If the control voltage is constant, the frequency is shifted by  $K_{VCO}V_{com}$

$$V_{com} = V_0$$

$$X(t) = V_{LO} \cos((\omega_{FR} + K_{VCO}V_0)t + \phi_0)$$

• The VCO is a frequency modulator  $V_{V_{i}}$

🚫 IP PARIS

#### **RF oscillators – Phase noise**

- Origin : internal noise of components constituting the oscillator example : amplifier thermal noise (use of a single transistor to minimize)

- Main effect : Random deviation of output wave frequency

$$X(t) = V_{LO} \cos(\omega_{LO}t + \Phi_n(t)) \qquad \Phi_n(t) : \text{ phase noise}$$

si  $|\Phi_n(t)| << 1$ ,  $X(t) \approx V_{LO} \{\cos(\omega_{LO}t) - \Phi_n(t)\sin(\omega_{LO}t)\}$

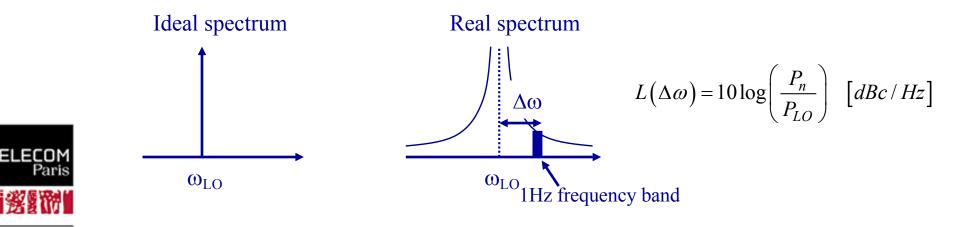

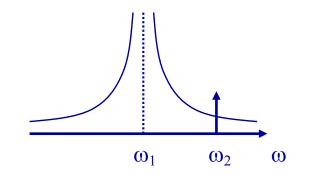

Frequency domain characterization for RF applications :

## **Spectral characterization**

• Thus, because of the different noise sources (thermal, 1/f...) the Power Spectral Density (PSD) spreads around  $f_0$

Example (DECT standard) : -97dBc/Hz @ 1,8 MHz

#### **Phase noise and Jitter**

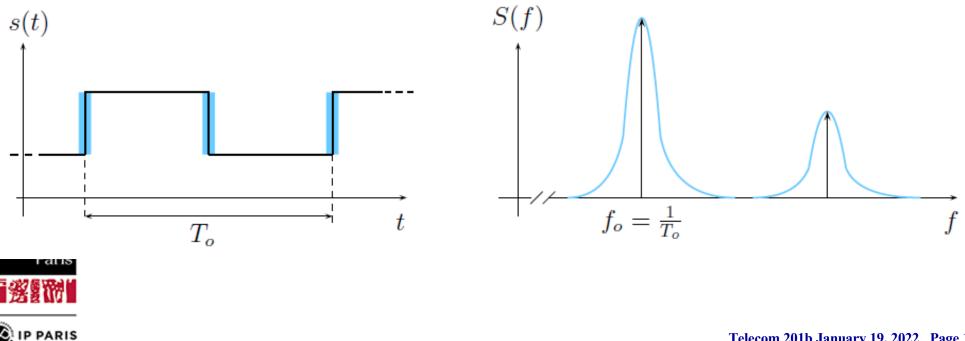

Phase noise and jitter are two manifestations of an unique phenomena : random fluctuations of the oscillator period.

Phase noise is associated to spectral representation whereas jitter is associated to time representation of these fluctuations

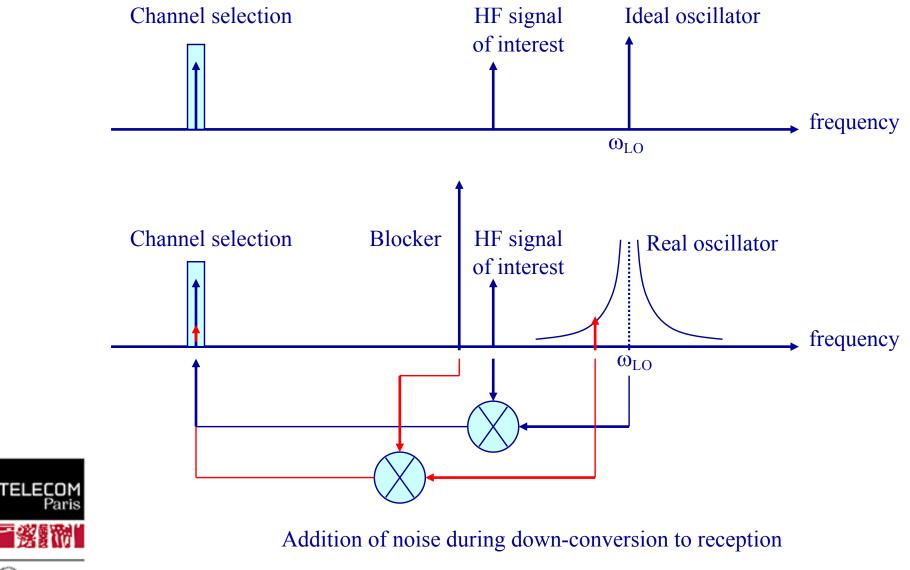

# **Phase noise – Reciprocal mixing**

## **Phase noise – Specification example**

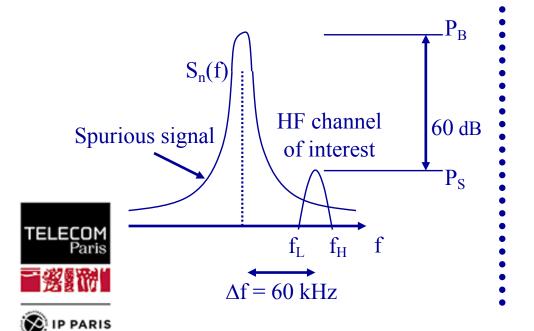

#### Real spectrum of the transmitter

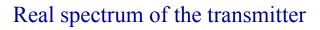

Adding noise during up-conversion to transmission

Calculation of a phase noise specification for the RF oscillator :

- Bandwidth of interest :  $f_H f_L = 30 \text{ kHz}$

- Assumption :  $S_n(\Delta f)$  is constant in this band

$S_n(\Delta f) = S_0 \quad [dBc/Hz]$

What is the maximum value of  $S_0$  that guarantees an SNR in the channel of interest greater than 15 dB?

## **Phase noise – Specification example**

Calculation of a phase noise specification for the RF oscillator :

- Bandwidth of interest :  $f_H f_L = 30 \text{ kHz}$

- Assumption :  $S_n(\Delta f)$  is constant in this band

$S_n(\Delta f) = S_0 \quad [dBc/Hz]$

What is the maximum value of  $S_0$  that guarantees an SNR in the channel of interest greater than 15 dB?

$SNR_{dB} = P_{S} - P_{N}$   $S_{0} = DSP_{N} - P_{B}$  $P_{N} = S_{0} + P_{B} + 10\log(f_{H} - f_{L})$

$S_0 = -SNR_{dB} - 60dB - 10log(f_H - f_L)$

The phase noise shall not exceed -120 dBc/Hz at 60 kHz offset

Digital Transceiver RF Font-end

RF oscillators

Indirect frequency synthesis

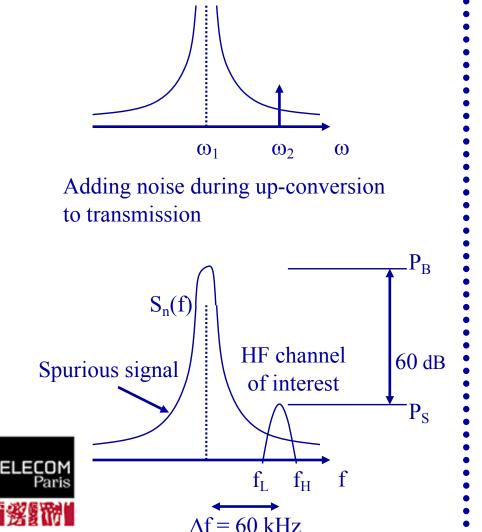

#### **PLL – Presentation**

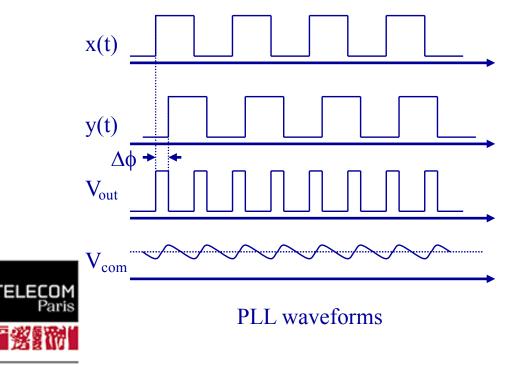

Basic Phase Locked Loop

The loop is locked when  $\Delta \Phi$  is constant, which corresponds to the equality of the input and output frequencies.

$$\omega_{y} = \omega_{FR} + K_{VCO}V_{com} = \omega_{x}$$

$$\Delta \Phi = \frac{V_{com}}{K_{DP}} = \frac{\omega_{x} - \omega_{FR}}{K_{DP} \cdot K_{VCO}}$$

The frequency are exactly equal !

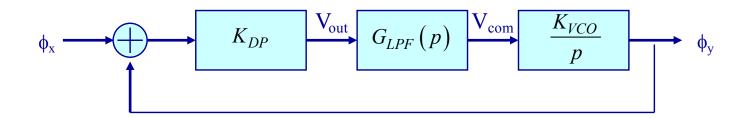

#### **PLL – Dynamic behavior**

$\Delta \Phi$

🚫 IP PARIS

Closed loop transfer function:  $H(p) = \frac{\Phi_y(p)}{\Phi_x(p)} = \frac{K G_{LPF}(p)}{p + K G_{LPF}(p)}$  avec  $K = K_{DP} K_{VCO}$

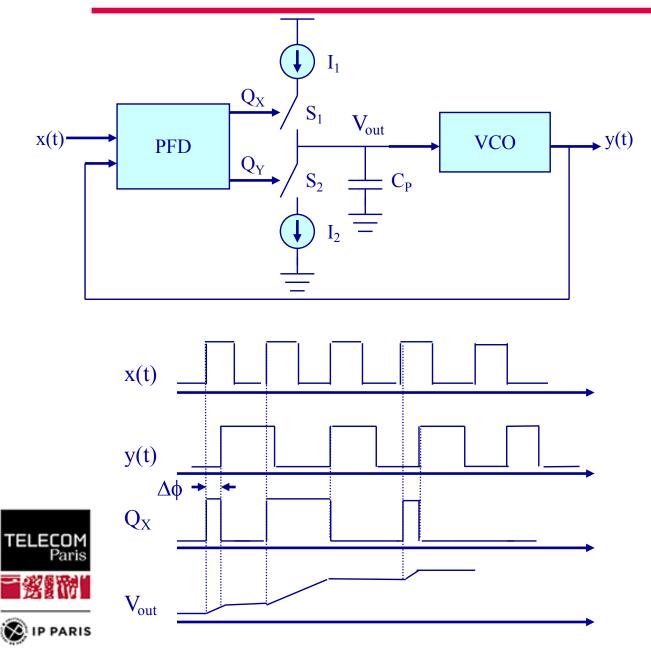

# **Charge Pump PLL**

Architecture with 3-state phase/frequency detector and charge pump circuit

$I_1 = I_2 = I$

Waveforms in CPPLL with  $\omega_x > \omega_y$  in closed loop :

$V_{out} \quad cons \tan t$   $\omega_y = \omega_{FR} + K_{VCO}V_{out} = \omega_x$   $\Delta \Phi = \Phi_x - \Phi_y = 0$  $Q_X = Q_Y = 0$

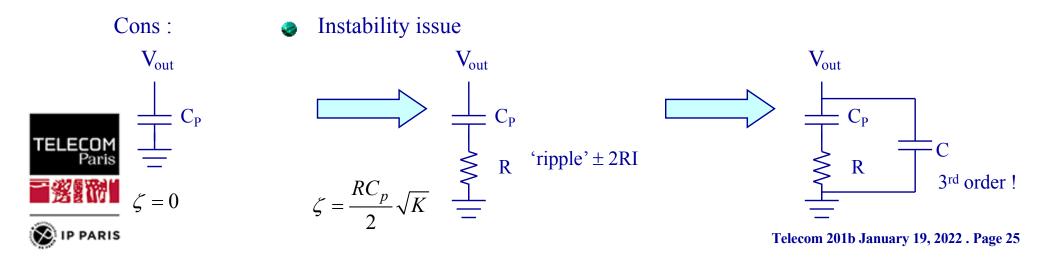

## **Charge Pump PLL**

Assuming that the bandwidth of the loop is much lower than the input frequency:

$$\phi_{x} \xrightarrow{K_{PFD}} p \xrightarrow{V_{out}} \xrightarrow{K_{VCO}} p \qquad \phi_{y}$$

$$p \qquad K_{PFD} = \frac{I}{2\pi C_{p}} \qquad H(p) = \frac{\Phi_{y}(p)}{\Phi_{x}(p)} = \frac{K}{p^{2} + K} \quad avec \quad K = K_{PFD}K_{VCO}$$

Main difference : two poles at zero in open loop

Pros :

- Maximum extension of the capture range,

- Increase of the locking speed,

- Zero static phase error (if ideal circuits).

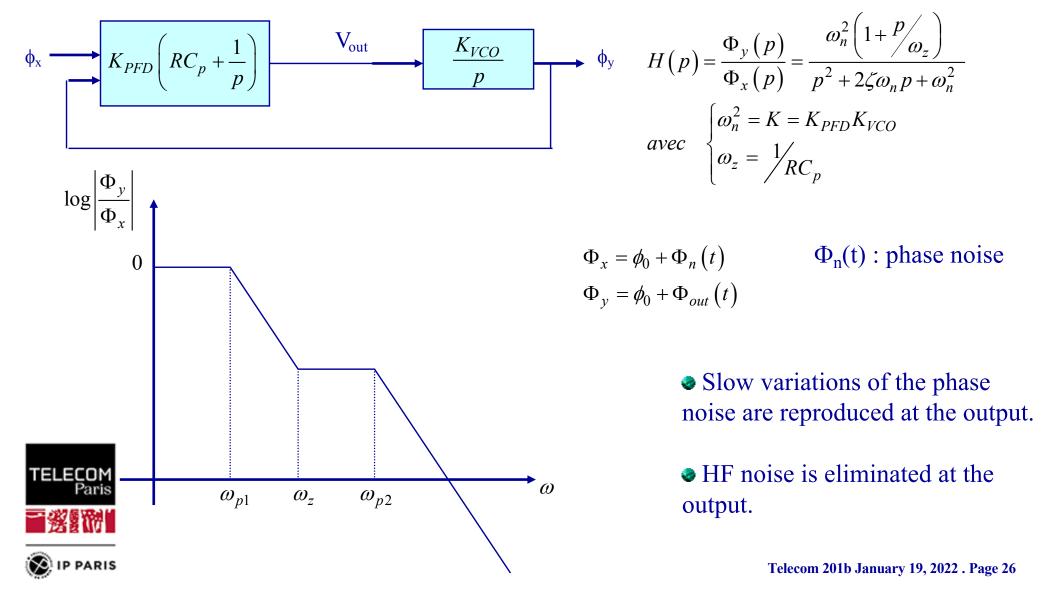

## **CPPLL – Input phase noise filtering**

Transfer function of a second-order CPPLL with a stabilization zero :

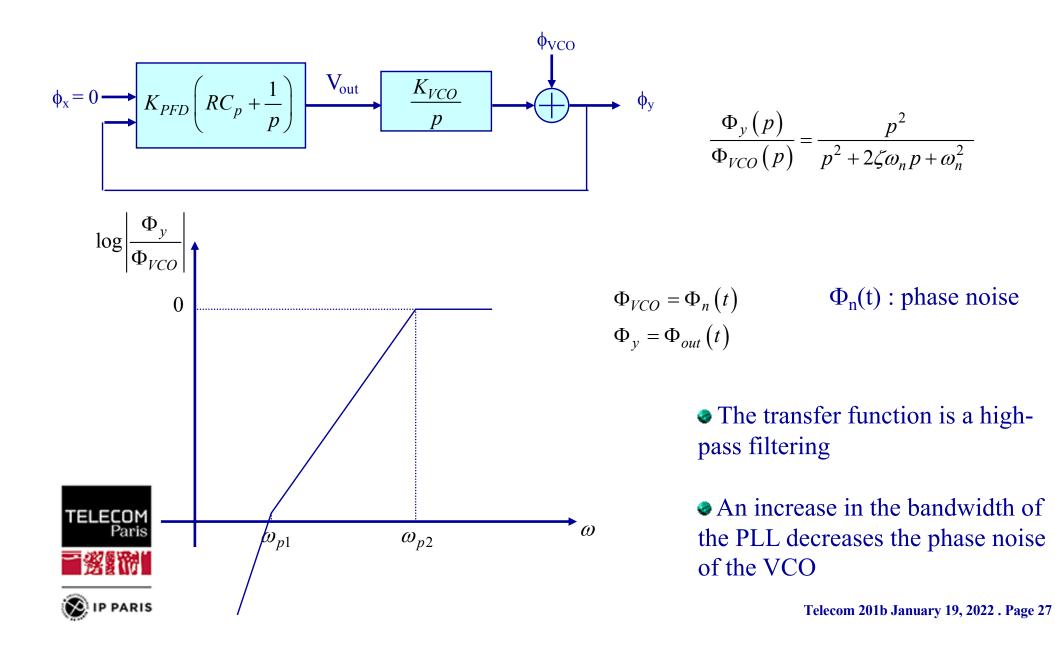

## **CPPLL – VCO phase noise filtering**

### **PLL – Applications**

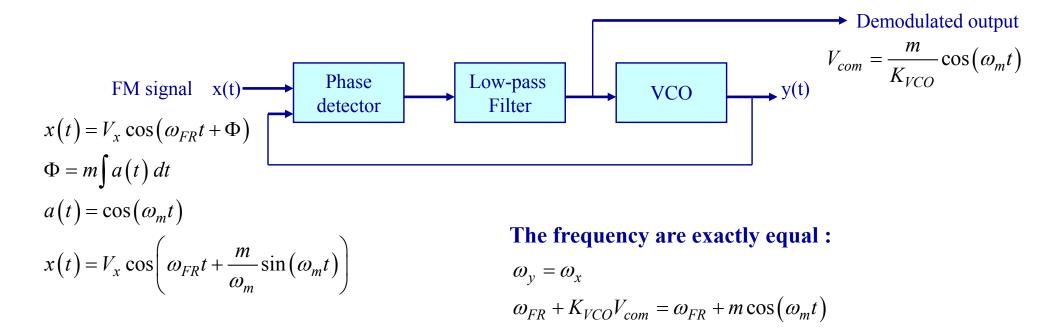

#### **RF signal demodulation**

#### **Important: Loop bandwidth large enough !**

Phase-locked loop for FM demodulator

🛞 IP PARIS

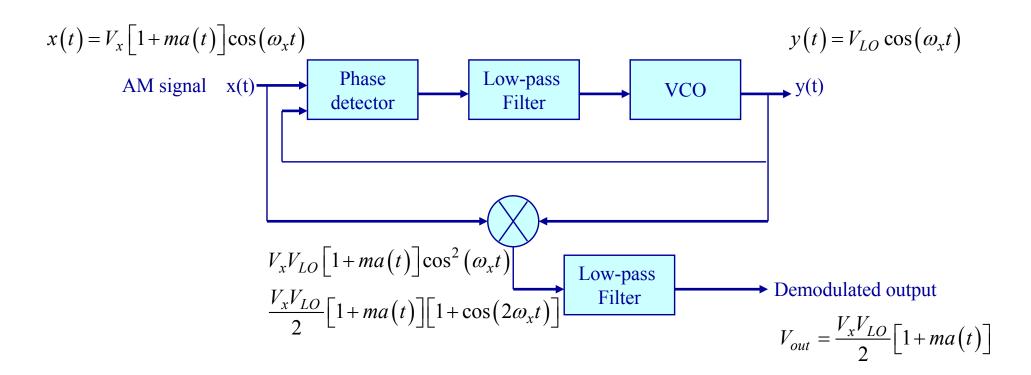

### **PLL – Applications**

#### **RF signal demodulation**

Phase-locked loop for AM coherent demodulator

🛞 IP PARIS

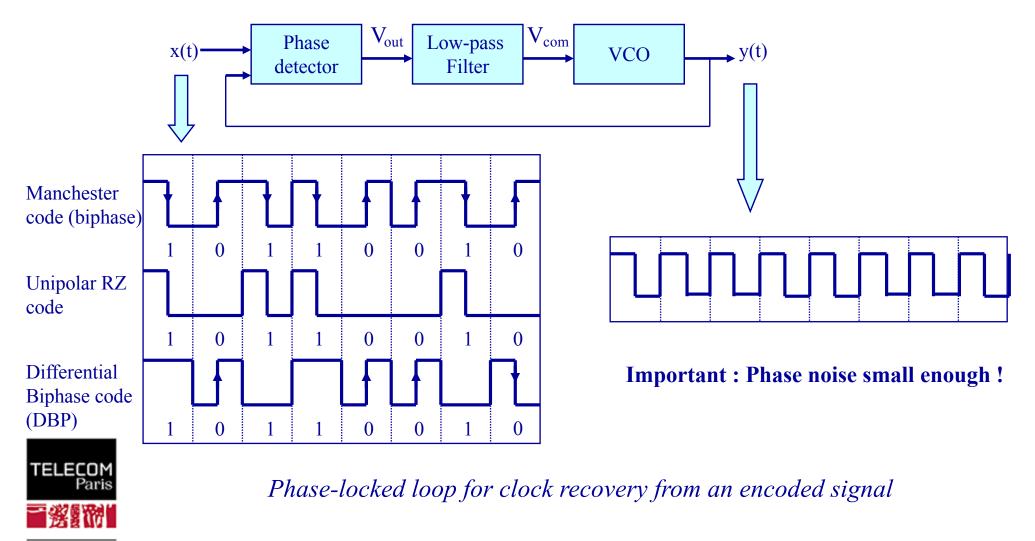

## **PLL – Applications**

#### **Clock recovery**

🛞 IP PARIS

#### **PLL - Conclusion**

Phase locked loops are key elements in digital communications systems. Their design and optimization are complex (trade-off between speed, precision, stability).

Main features are :

- Locking and Capture Ranges

- Agility (locking speed)

- Phase noise

- Bandwidth

- Settling time

#### Major application for the RF front end

**RF frequency synthesis** : RF oscillator, PLL

$f_{LO} = f_0 + k f_{ch}$  Channel selection

#### Digital Transceiver RF Font-end

RF oscillators

PLLs

Indirect frequency synthesis

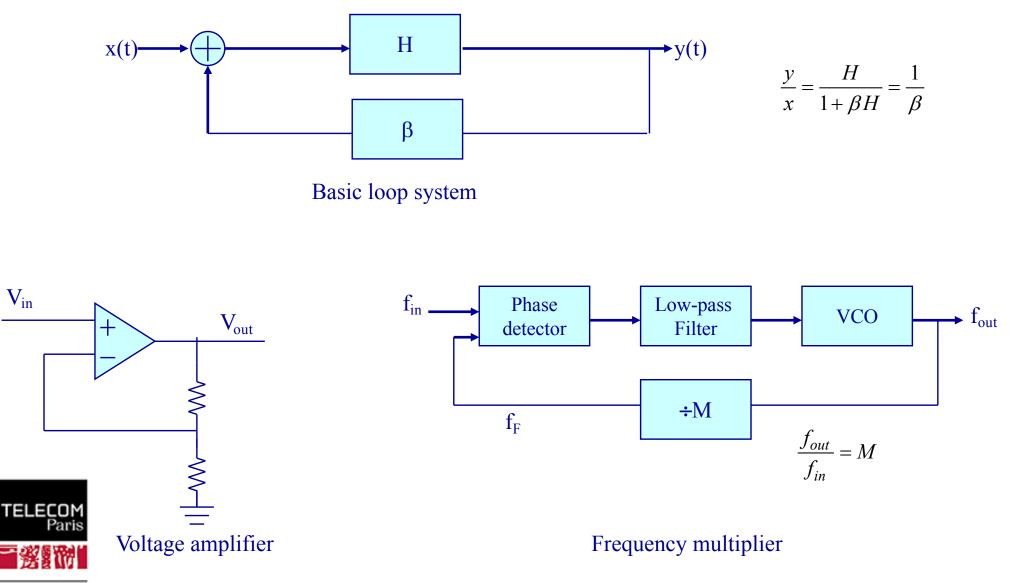

## **Frequency multiplication**

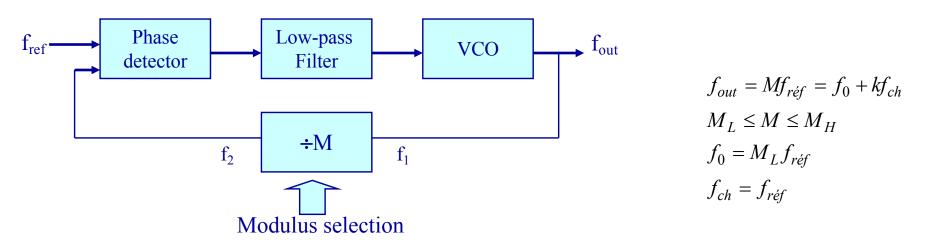

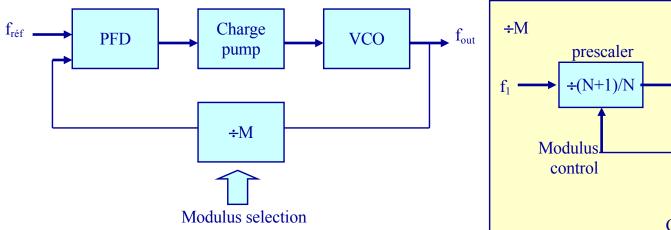

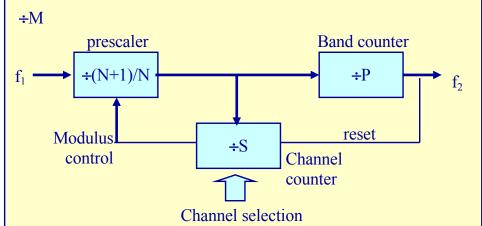

## **Integer Modulus Synthesizer**

The reference input frequency must be equal to the channel spacing.

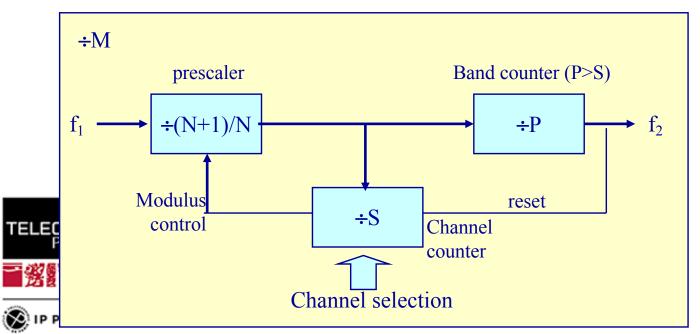

Frequency divider by pulse counting

One output cycle occurs at the end of (N + 1) \* S + N \* (P-S) input cycles.

$$f_2 = \frac{f_1}{NP + S}$$

# **Integer Modulus Synthesizer**

- Main advantage: architecture simplicity

- *Implementation* in RF system :

Band counter, channel counter, PFD, charge pump

Main drawback:

The reference frequency has a small value.

The bandwidth of PLLs is limited to 1/10 of the input frequency to ensure stability

a single die in deeply submicronic CMOS technology

ex : GSM inter-channel spacing : 200kHz Settling time 100 μs or more

ELECO

Paris

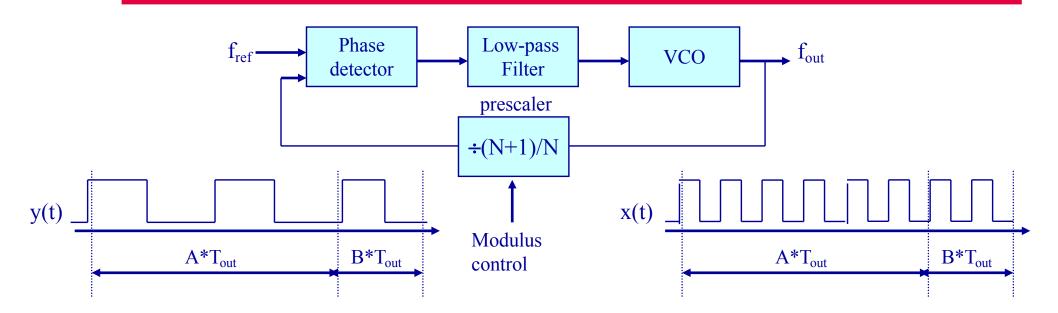

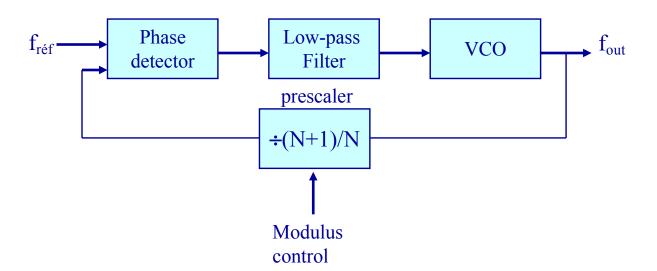

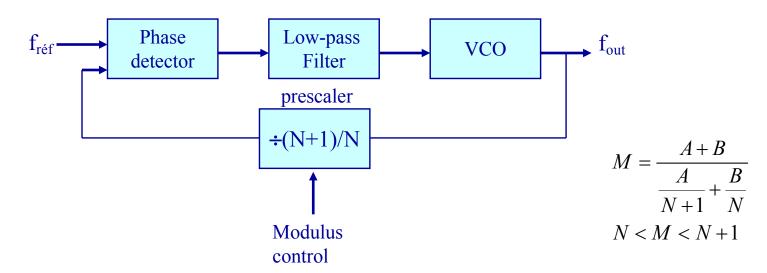

# **Fractional Modulus Synthesizer**

Number of pulses during the time  $(A+B)T_{out}$ : A/(N+1) + B/N'Average' or equivalent frequency of y(t) :  $(A/(N+1) + B/N) / ((A+B) T_{out})$  $= f_{out} / M$

🚫 IP PARIS

Use of a two-modulus frequency divider

Locked loop :  $f_{r\acute{e}f} = f_{out} / M$   $f_{out} = M * f_{r\acute{e}f}$

$$M = \frac{A+B}{\frac{A}{N+1} + \frac{B}{N}}$$

$$N < M < N+1$$

# **Fractional Modulus Synthesizer**

#### EXAMPLE :

Let's Consider a synthesizer for which the reference frequency is provided by a 1MHz oscillator. The expected output frequency is:

$$f_{out} = f_0 + k f_{ch}$$

with  $f_0=10$  MHz and  $f_{ch}=100$ kHz for k= 0, 1, 2,...9, 10. What is the value of N? What are the minimum possible values for A and B to address the different channels?

$M = \frac{A+B}{\frac{A}{N+1} + \frac{B}{N}}$ N < M < N+1

IP PARIS

## **Fractional Modulus Synthesizer**

#### EXAMPLE :

Let's Consider a synthesizer for which the reference frequency is provided by a 1MHz oscillator. The expected output frequency is:

| $f_{out} = f_0 + k f_{ch}$                                   | N=10            |                 |

|--------------------------------------------------------------|-----------------|-----------------|

|                                                              | Pour k=0, A=0   | k=10, B=0       |

| with $f_0=10$ MHz and $f_{ch}=100$ kHz for k= 0, 1, 2,9, 10. | k=1, A=11, B=90 | k=2, A=22, B=80 |

| What is the value of N?                                      | k=3, A=33, B=70 | k=4, A=44, B=60 |

| What are the minimum possible values for A and B             | k=5, A=55, B=50 | k=6, A=66, B=40 |

| to address the different channels?                           | k=7, A=77, B=30 | k=8, A=88, B=20 |

|                                                              | k=9, A=99, B=10 |                 |