#### **UE TELECOM201 - 2021-2022**

La Conversion Numérique/Analogique La Conversion Analogique/Numérique

#### Patricia DESGREYS

TELECOM Paris Département Communications et Electronique <u>mailto:patricia.desgreys@telecom-paris.fr</u>

# La conversion numérique analogique

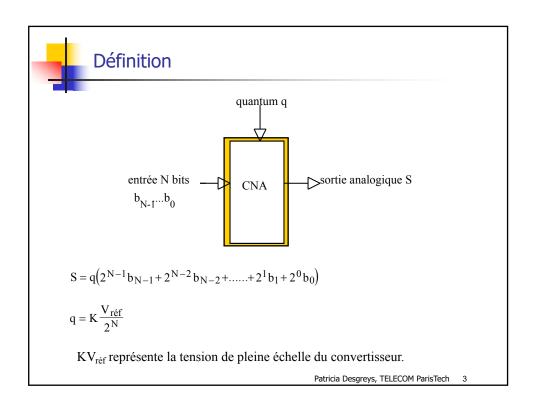

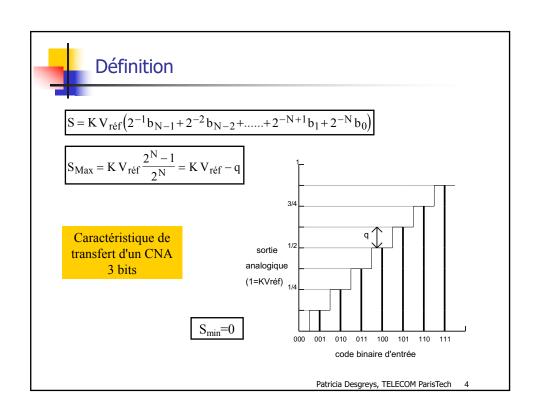

- **D**éfinition

- Principales caractéristiques

- Test des CNA

- CNA parallèles à réseau pondéré

- CNA parallèles haute résolution

- CNA algorithmiques

- **Conclusion**

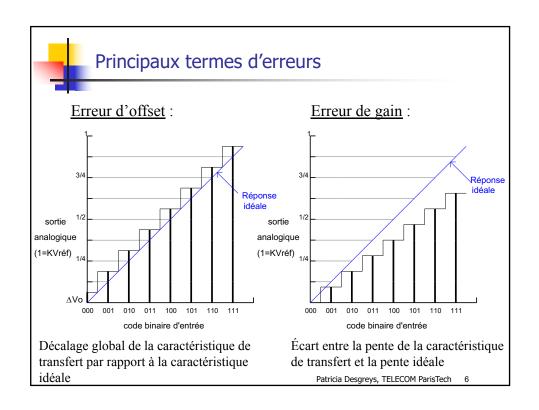

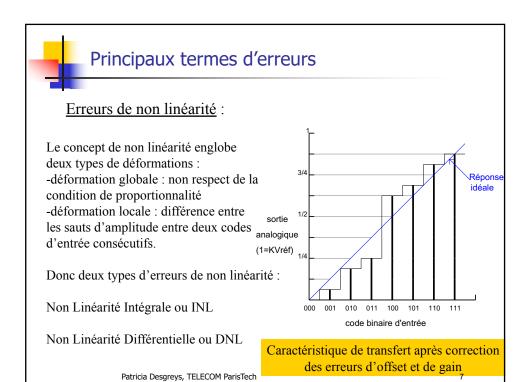

## Principales caractéristiques

#### Résolution:

plus petite variation de la tension de sortie en réponse à un changement du code numérique d'entrée ↔ nombre de niveaux accessibles en sortie

Résolution du convertisseur N bits :  $q = K \frac{V_{r\acute{e}f}}{2^N}$

Exemple : N=16 bits et PE=2V  $\rightarrow$  q=30 $\mu$ V

#### Précision:

mesure de l'écart entre la valeur obtenue réellement et la valeur prédite théoriquement

$Pr\'{e}cision \ du \ convertisseur \ N \ bits: \qquad \Delta V_e \leq K \frac{V_{r\'{e}f}}{2^{N+1}}$

La résolution et la précision ne sont pas nécessairement égales

Patricia Desgreys, TELECOM ParisTech

5

## Principales caractéristiques

#### Monotonicité:

caractère selon lequel la sortie analogique est continûment croissante pour une variation croissante du mot numérique d'entrée.

important lorsque le convertisseur referme une boucle de contre réaction.

#### <u>Gamme d'utilisation</u>:

Les performances d'un CNA évoluent avec le temps, la température, et la tension d'alimentation. Donc, le gain, l'offset, les non linéarités et la monotonicité doivent être spécifiés dans une gamme de température et de tension d'alimentation.

Patricia Desgreys, TELECOM ParisTech

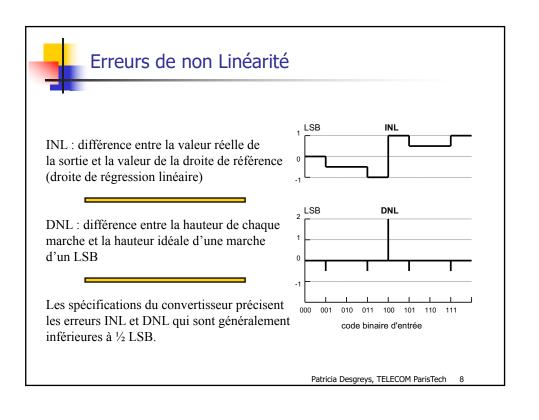

#### Principales caractéristiques

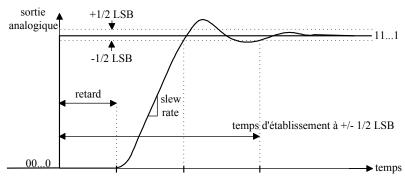

#### Temps d'établissement:

temps au bout duquel la sortie analogique (soit en tension, soit en courant) est comprise dans une bande définie (typiquement ±1/2 LSB) autour de sa valeur finale, en réponse à un changement de code pleine échelle en entrée.

#### Principales caractéristiques

#### Bande passante du convertisseur :

Le temps nécessaire au traitement des données à l'intérieur des convertisseurs fixe une fréquence maximale de fonctionnement ou taux d'échantillonnage limite.

Lorsque l'application nécessite seulement que la sortie analogique soit comprise dans une bande définie autour de sa valeur finale avant que le nouveau code numérique d'entrée puisse être traité :

$$taux \ de \ conversion \ N \ / \ A \ max = \frac{1}{temps \ d' \'etablissement}$$

Plus généralement, la procédure d'évaluation de la bande passante du convertisseur s'appuie sur le tracé du nombre effectif de bit du convertisseur en fonction de la fréquence du signal d'entrée. Dès que le nombre effectif de bits chute d'1/2 par rapport à la résolution DC, la précision nominale n'est plus garantie et la limite de la bande passante du convertisseur est atteinte.

Patricia Desgreys, TELECOM ParisTech

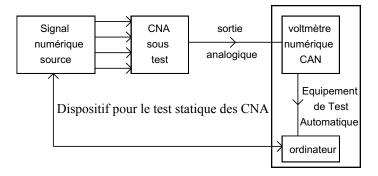

## Test des caractéristiques statiques

La précision du voltmètre numérique doit être bien plus importante que la précision du convertisseur sous test.

Le test des caractéristiques statiques doit donc être effectué pour plusieurs températures et plusieurs tensions d'alimentation (minimale, nominale, maximale).

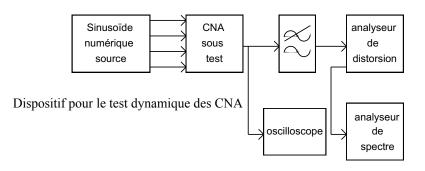

## Test des performances dynamiques par FFT

Plage dynamique sans bruit (SFDR) : différence en dB entre l'amplitude du fondamental et l'amplitude de l'harmonique la plus importante.

$ENOB = \frac{SNR_{dB} - 1.76}{}$ Nombre effectif de bits (ENOB): 6.02

Patricia Desgreys, TELECOM ParisTech

# La conversion numérique analogique

Définition

Principales caractéristiques

Test des CNA

CNA parallèles à réseau pondéré

CNA parallèles haute résolution

CNA algorithmiques

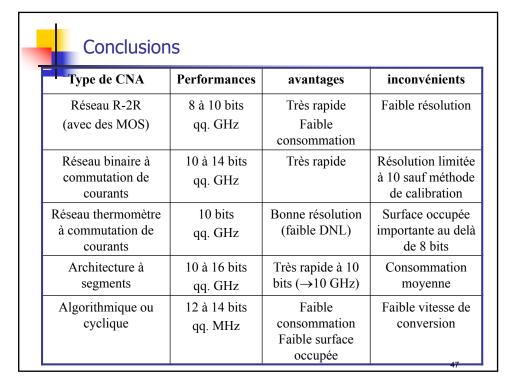

Conclusion

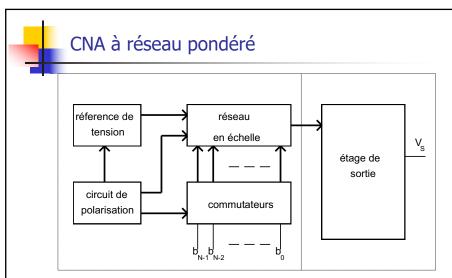

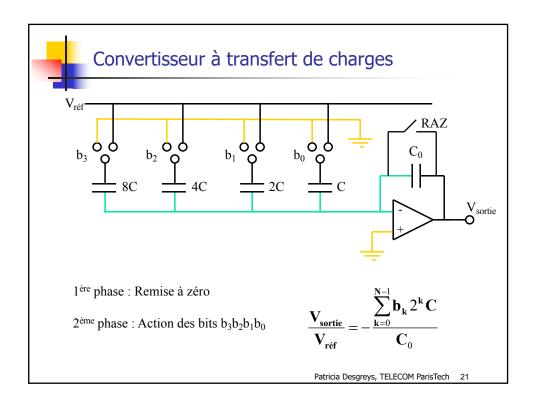

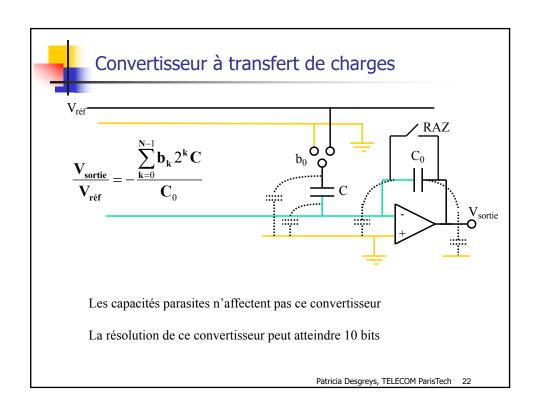

*Principe* : La sortie est la somme de références analogiques pondérées (réseau binaire) sélectionnées par les bits du mot numérique d'entrée. Les références sont des sources calibrées de courant, de tension ou de charges.

Avantage: rapidité – bande passante accessible = 500 MHz

## Convertisseur à éléments unités

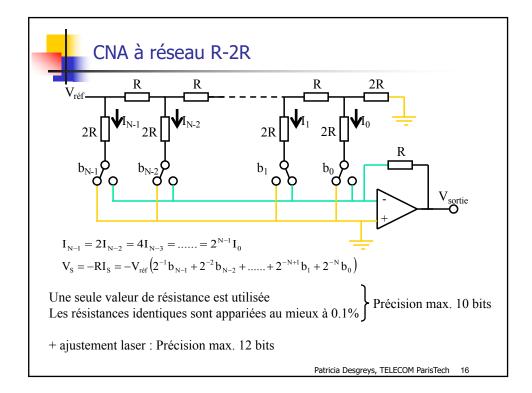

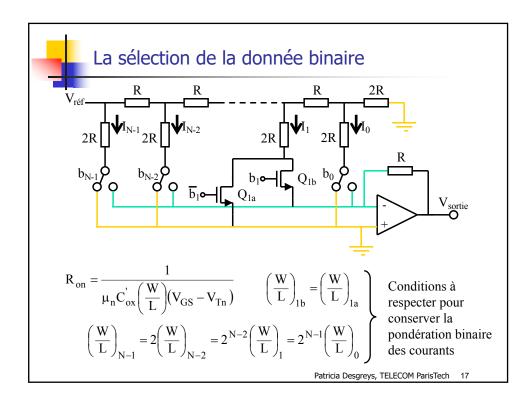

Dans les technologies MOS standards, les résistances sont trop imprécises

Des performances supérieures sont obtenues avec des circuits qui exploitent la mise en parallèle d'un grand nombre d'éléments (capacités ou transistors) unités identiques.

*Inconvénient* : le nombre d'éléments augmente exponentiellement avec le nombre de bits.

Avantage : Les bits de rangs élevés correspondent à la mise en parallèle d'un nombre très important d'éléments unités. La dispersion entre les éléments est alors moyennée et donc éliminée.

$2 \text{ types de convertisseurs pondérés à éléments unités} \begin{cases} \text{Réseau capacitif} \\ \text{Réseau de transistors} \end{cases}$

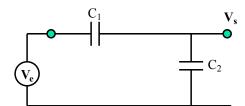

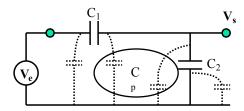

## Le diviseur capacitif

$$\frac{V_{s}}{V_{e}} = \frac{C_{1}}{C_{1} + C_{2}}$$

Avantages: La consommation est fortement réduite puisque aucun courant DC ne circule dans le diviseur.

Les comportements DC et AC peuvent être contrôlés indépendamment.

Patricia Desgreys, TELECOM ParisTech 19

## Le diviseur capacitif

$$\frac{V_s}{V_e} = \frac{C_1}{C_1 + C_2}$$

Avantages: La consommation est fortement réduite puisque aucun courant DC ne circule dans le diviseur.

Les comportements DC et AC peuvent être contrôlés indépendamment.

Inconvénient : Les diviseurs capacitifs sont fortement sensibles aux capacités parasites V C.

$\frac{V_s}{V_e} = \frac{C_1}{C_1 + C_2 + C_p}$

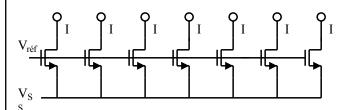

## Réseau à transistors

Une rangée de sources de courants unitaires peuvent jouer le même rôle qu'une rangée de capacités unités.

Deux types de combinaisons sont réalisés

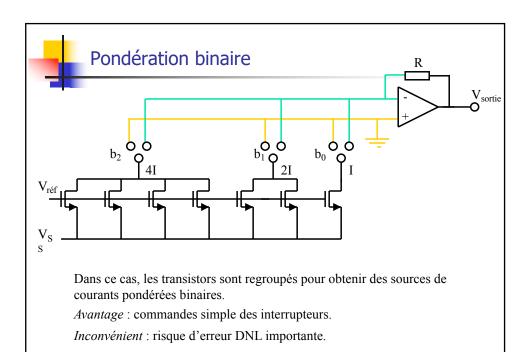

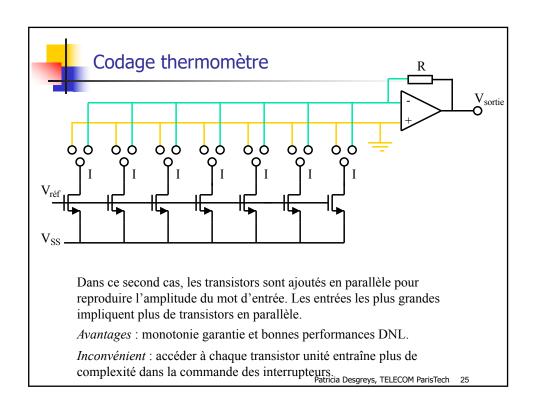

Pondération binaire

Codage thermomètre

Les réseaux de transistors utilisent uniquement des transistors identiques. Les défauts d'appariement entre transistors identiques limitent la précision des CNA à réseau à transistors à 10 bits.

Patricia Desgreys, TELECOM ParisTech 23

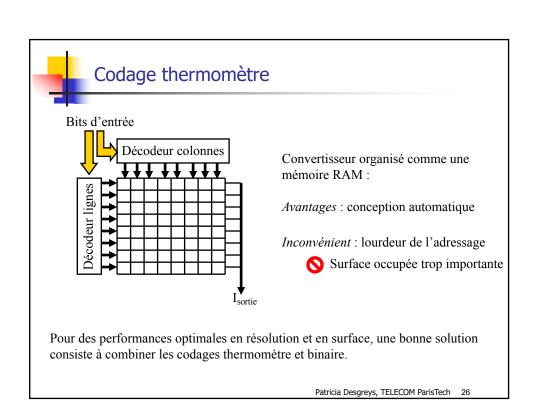

## Codage thermomètre partiel

| Résolution             | 10 bits    |

|------------------------|------------|

| Technologie            | CMOS 90 nm |

| INL                    | 0,41 LSB   |

| DNL                    | -0,031 LSB |

|                        |            |

| Tension d'alimentation | 1,2 V      |

10 bit current steering DAC in 90 nm technology, Aerospace and Electronics Conference, NAECON 2014 - IEEE National, Issue Date: 24-27 June 2014, Written by: Moody, T.; Saiyu Ren; Ewing, R.

| Fréquence du signal d'entrée | Fréquence<br>d'échantillonnage | SFDR  |

|------------------------------|--------------------------------|-------|

| 250 MHz                      | 1 GS/s                         | 69 dB |

Patricia Desgreys, TELECOM ParisTech 27

## Limitations des CNA à réseau pondéré

Les CNA en échelle ne sont pas appropriés au delà de 10 bits car Les conditions d'appariement sont irréalisables

- imprécision trop importante les résistances dans le réseau R-2R

- onombre d'éléments trop important (croissance exponentielle) pour la conversion basée sur des éléments unitaires identiques

Deux techniques pour la conversion NA parallèle haute résolution :

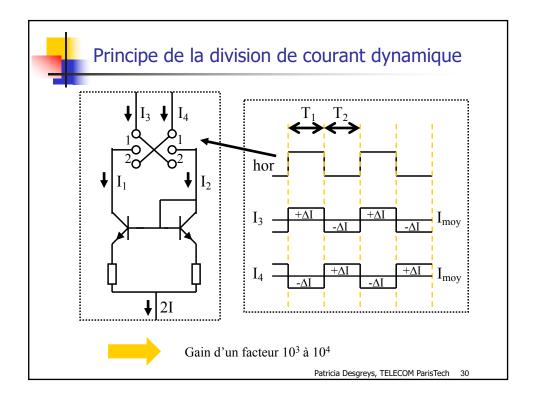

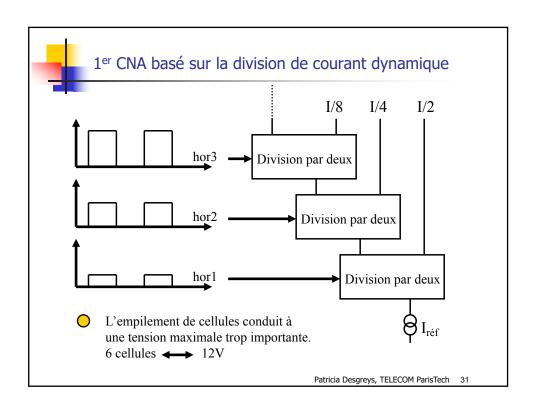

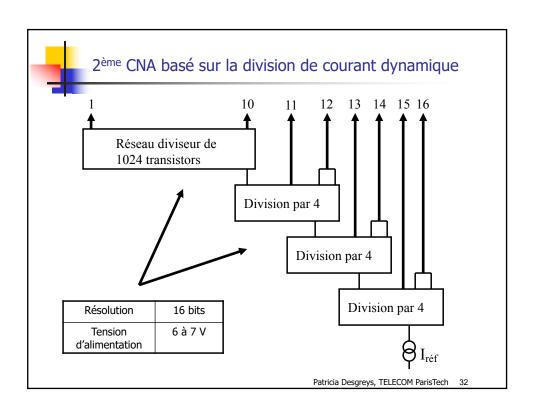

Division de courant dynamique

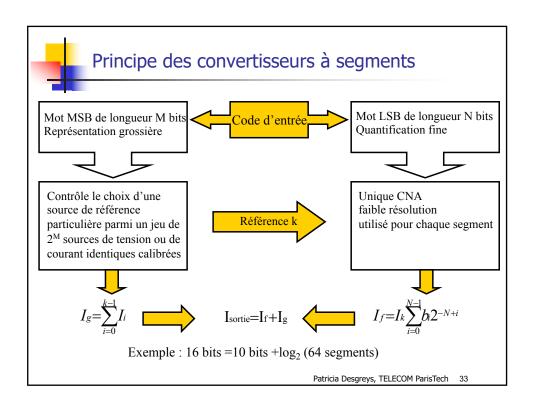

Convertisseurs à segments (ou par morceaux)

# La conversion numérique analogique

Définition

Principales caractéristiques

Test des CNA

CNA parallèles à réseau pondéré

#### CNA parallèles haute résolution

CNA algorithmiques

Conclusion

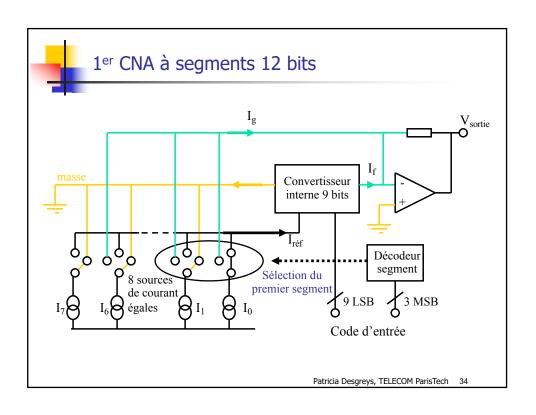

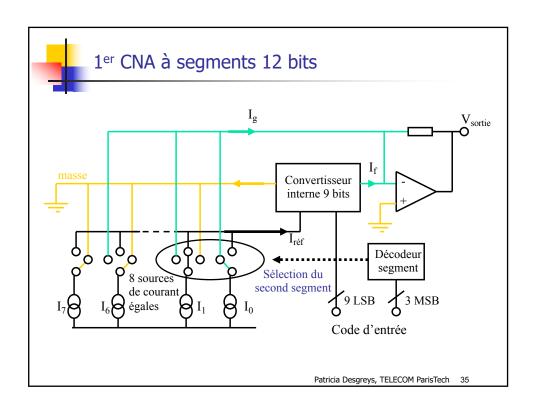

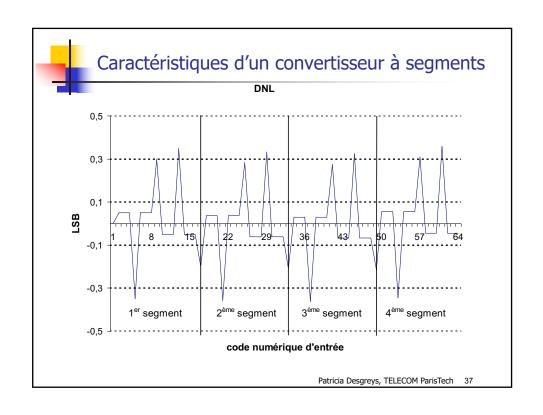

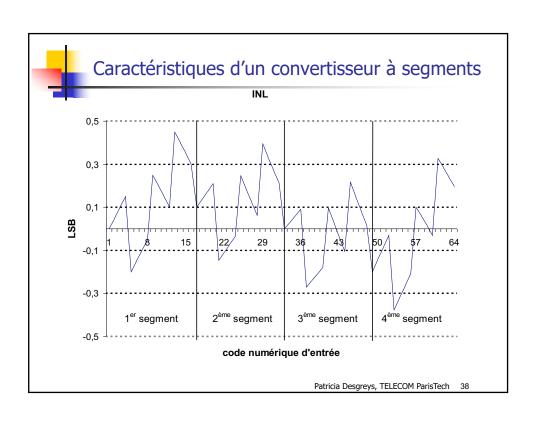

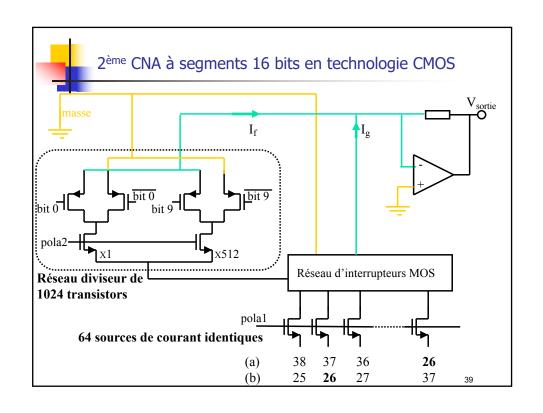

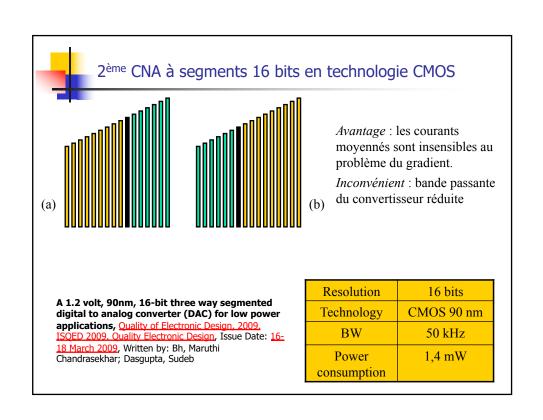

## Caractéristiques d'un convertisseur à segments

La caractéristique de transfert du convertisseur est le résultat de plusieurs caractéristiques de transfert basse résolution concaténées

Le passage d'un segment à un autre se traduit par l'ajout de  $I_k$  dans  $I_g$  et le passage de la valeur  $I_k$ -q à 0 pour  $I_f$ .

Les segments sont parfaitement accolés

En revanche, comme chaque référence contrôle le gain d'un segment, la caractéristique de transfert totale montre en général de petites variations de pente car les courants de référence ne sont pas parfaitement égaux

# La conversion numérique analogique

Définition

Principales caractéristiques

Test des CNA

CNA parallèles à réseau pondéré

CNA parallèles haute résolution

#### **CNA** algorithmiques

Conclusion

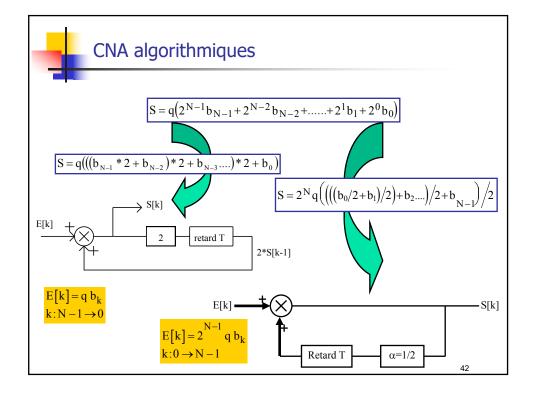

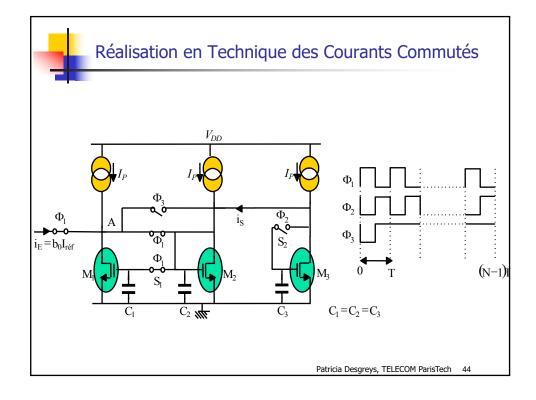

## CNA algorithmiques

<u>Conclusion</u>: trois opérations élémentaires constituent un CNA algorithmique:

1. Une addition

2. Une multiplication ou une division par deux

3. Un retard d'une période

<u>Avantages</u>: faible surface occupée

faible consommation

<u>Inconvénients</u> : faible vitesse de conversion

précision limitée à 12-14 bits

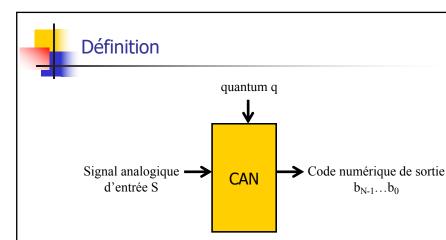

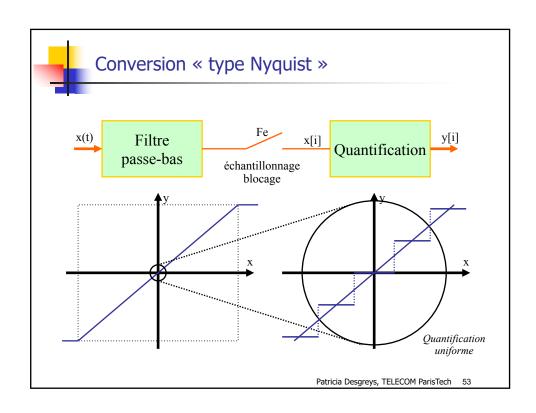

# La conversion analogique numérique

- **D**éfinition

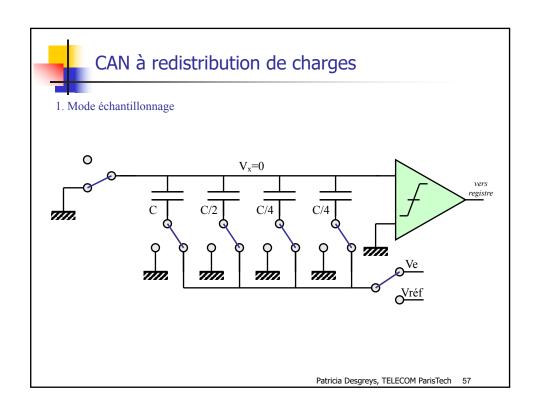

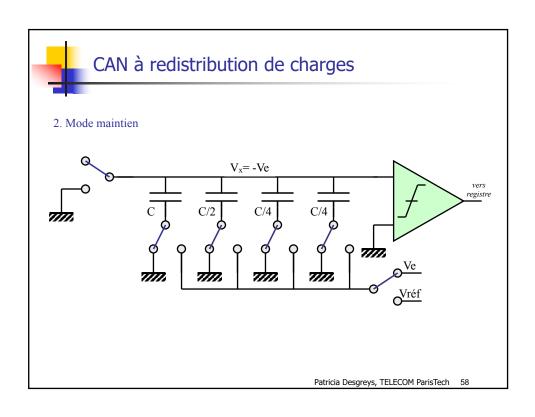

- Échantillonnage blocage

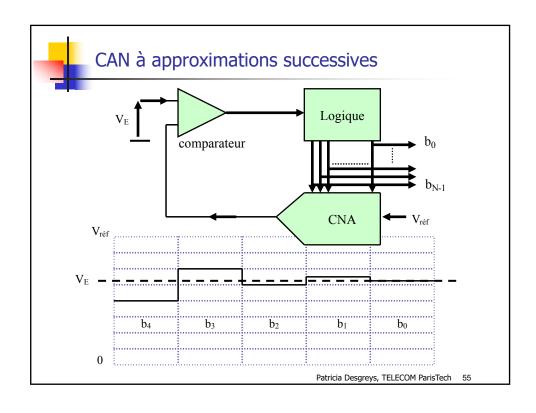

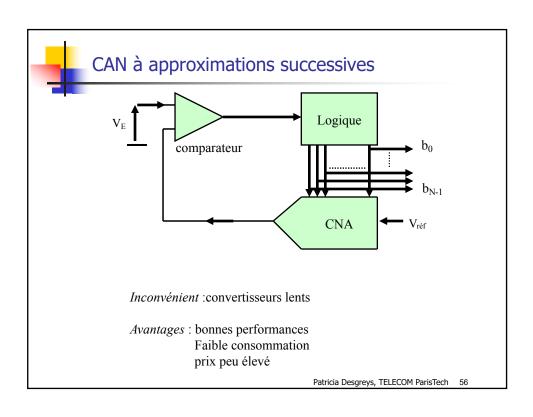

- CAN à approximations successives

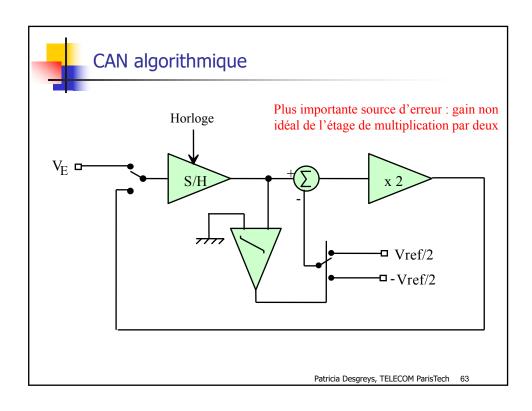

- **CAN** algorithmiques

- **CAN** flash

- Technique du sur échantillonnage et conversion  $\Sigma\Delta$

**■ADC** performance: State-of-the-art

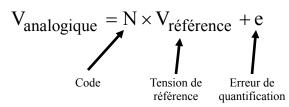

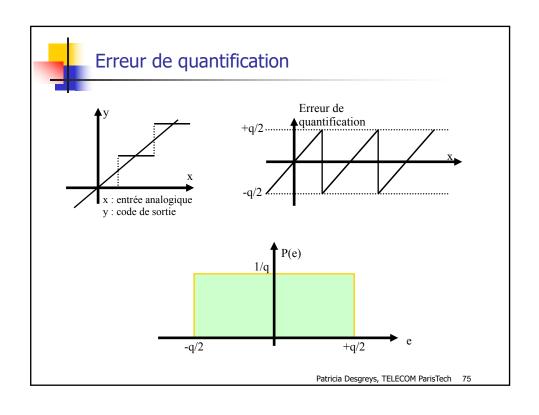

$$S = q(2^{N-1}b_{N-1} + 2^{N-2}b_{N-2} + \dots + 2^{1}b_{1} + 2^{0}b_{0}) + e$$

Principales caractéristiques : résolution, précision, erreur d'offset, erreur de gain, INL, DNL...

Nécessité d'un circuit échantillonneur bloqueur

Patricia Desgreys, TELECOM ParisTech 49

$b_{N\text{-}1}...b_0$

## Equation caractéristique

$$-\frac{q}{2} \le e < +\frac{q}{2}$$

q: pas de quantification

N : code numérique sur n bits : {  $b_{n\text{-}1},\,...,\,b_0\}$ n : résolution du convertisseur

$$N = \frac{b_{n-1}}{2} + \frac{b_{n-2}}{2^2} + \dots + \frac{b_0}{2^n}$$

$$q = \frac{V_{r\acute{e}f\acute{e}rence}}{2^n}$$

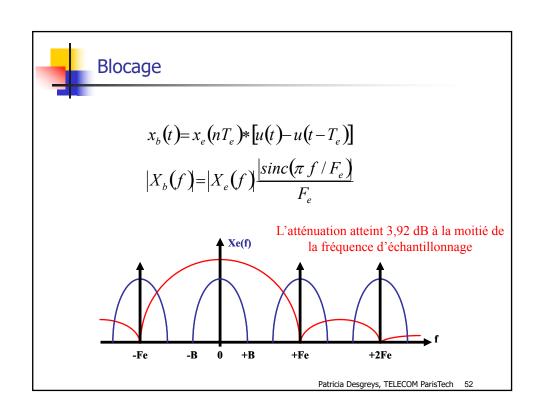

Échantillonnage

$$x_{e}(t) = x(t) \sum_{n=-\infty}^{n=+\infty} \delta(t - nT_{e}) = \sum_{n=-\infty}^{n=+\infty} x(nT_{e}) \delta(t - nT_{e})$$

$$X_{e}(f) = \frac{1}{T_{e}} X(f) * \sum_{n=-\infty}^{n=+\infty} \delta(f - nF_{e}) = \frac{1}{T_{e}} \sum_{n=-\infty}^{n=+\infty} X(f - nF_{e})$$

Filtre anti repliement:

$$n = \frac{DR_{dB}}{20 \log_{10} \left(\frac{F_{e}}{2F_{e}}\right)}$$

Patricia Desgreys, TELECOM ParisTech 51

# La conversion analogique numérique

Définition

Échantillonnage blocage

CAN à approximations successives

CAN algorithmiques

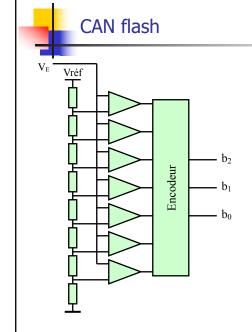

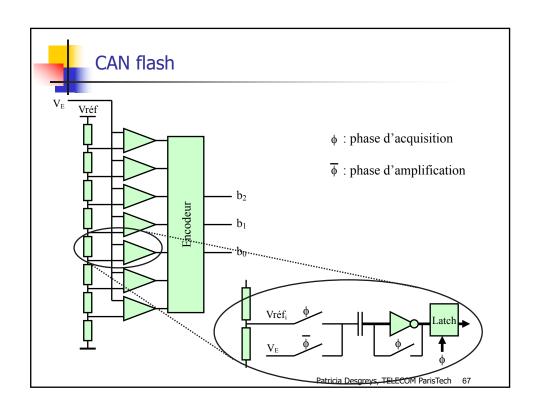

#### **CAN flash**

Technique du sur échantillonnage et conversion  $\Sigma\Delta$

**□ADC** performance: State-of-the-art

#### Conversion AN rapide

Fréquences d'échantillonnage recherchées : qq. MS/s à qq. **100 MS/s** *Applications* : télécommunications, vidéo, imagerie médicale, radars, analyseurs de réseaux.

nécessité d'une conversion parallèle en un seul cycle d'horloge

équivalent AN des CNA à réseau codé thermomètre

Les seuls convertisseurs qui fonctionnement vraiment en un cycle d'horloge sont les convertisseurs flash.

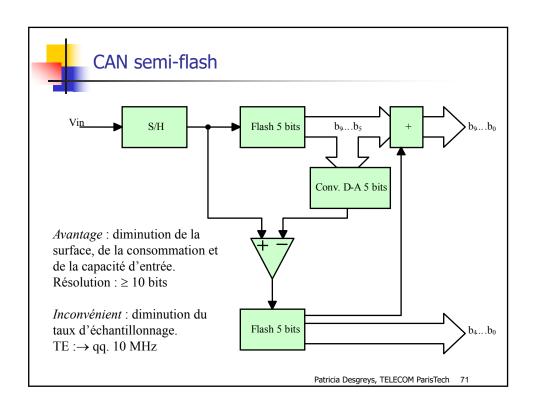

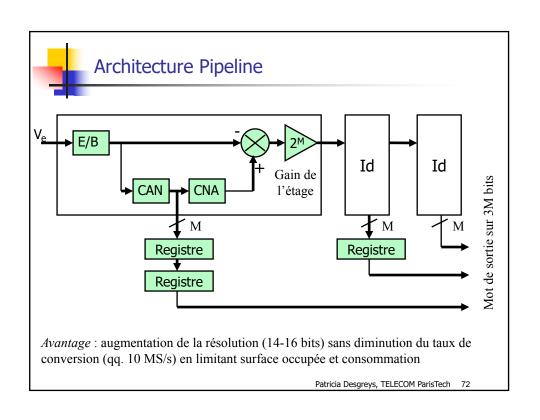

D'autres convertisseurs (convertisseurs semi-flash, convertisseurs pipeline) combinent des convertisseurs flash faible résolution et des architectures algorithmiques pour diminuer la consommation au prix de 2 ou 3 cycles d'horloges.

Patricia Desgreys, TELECOM ParisTech 65

Avantage : pas d'échantillonneur bloqueur → plus de rapidité.

*Inconvénient* : un banc de comparateurs → consommation et distorsion non linéaire.

Puisque la capacité d'entrée très élevée (qq. 10 pF) des comparateurs est couplée à l'impédance du générateur d'entrée et que la fréquence du signal d'entrée est élevée, des courants importants circulent dans les terminaux d'entrée des comparateurs.

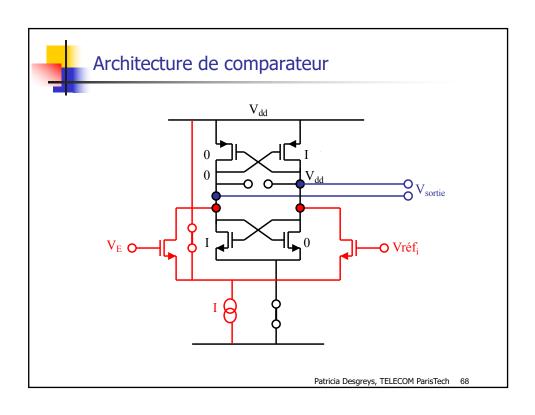

#### Impact des non-idéalités du comparateur

**Imperfection statique** : les offsets des bascules sont assez importants (50 mV) et divisé par le gain de la paire différentielle, **l'erreur d'offset** s'étale entre 5 et 20 mV en entrée.

- Ceci se traduit par une erreur DNL importante, définit la plus petite discrimination et limite donc la résolution (6 ou 7 bits).

- Un contrôle approprié des offsets des différentes paires différentielles permet d'atteindre une résolution de 10 bits.

#### **Imperfections dynamiques:**

- L'amplificateur différentiel fonctionne en linéaire et en non linéaire. Sa bande passante est limitée. Un **retard** très variable et dépendant du signal est donc observé

- L'état logique précédant une nouvelle comparaison influe sur l'entrée, créant une erreur d'hystérésis ou offset dynamique ou **bruit de kick back** (contrecoup).

Patricia Desgreys, TELECOM ParisTech 69

## Autres sources de distorsion non linéaire

- L'échelle de références définit également la plus petite discrimination et limite donc la résolution. Le polysilicium présente une résistance de qq. 10 Ω/□ mais la reproductibilité n'est pas très satisfaisante.

L'impact est direct sur l'erreur INL mais l'erreur DNL est négligeable et aucune erreur de monotonie n'est engendrée.

Résolution max. : 8 bits (ou 10 bits si ajustement laser)

- → Jitter d'horloge

Bruit des comparateurs

Layout

décalages de phase aléatoires ou dépendants de la position

# Architectures à résolution limitée

| Type de CAN                | Performances                | avantages                                                       | inconvénients                |

|----------------------------|-----------------------------|-----------------------------------------------------------------|------------------------------|

| Approximations successives | 10 à 12 bits<br>qq. MHz     | Faible coût                                                     | Faible vitesse de conversion |

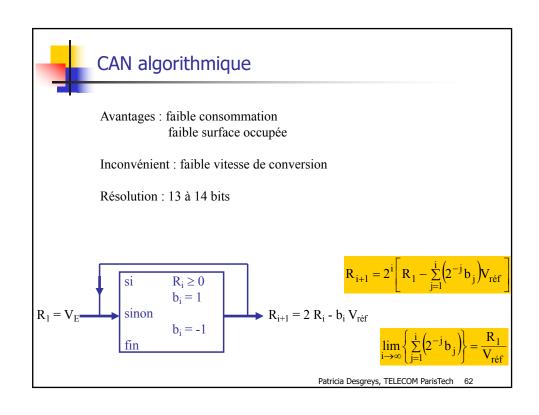

| Algorithmique ou cyclique  | 12 à 14 bits<br>qq. MHz     | Faible consommation<br>Faible surface occupée                   | Faible vitesse de conversion |

| Flash                      | 8 à 10 bits<br>qq. GHz      | Très rapide                                                     | Forte consommation           |

| Semi-flash                 | 12 à 14 bits<br>qq. 100 MHz | Consommation, surface occupée et vitesse de conversion moyennes |                              |

| Pipeline                   | 14 à 16 bits<br>qq. 100 MHz | Bonne résolution,<br>Faible consommation pour 10 bits           |                              |

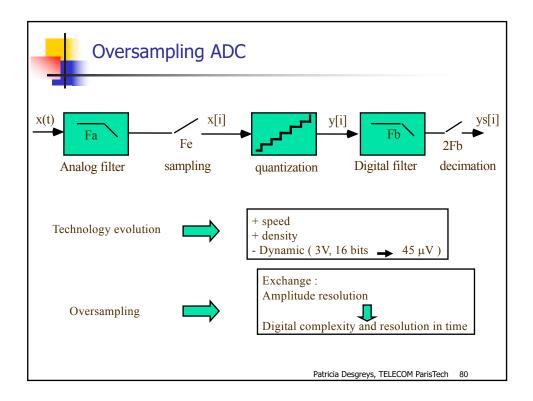

Pour tous ces types de convertisseurs, la précision est limitée par la dispersion sur les composants. Avec une technologie CMOS standard, la dispersion sur les capacités ou résistances intégrées limitent la précision à 10-12 bits (+2 si ajustement laser). 73

# La conversion analogique numérique

Définition

Échantillonnage blocage

CAN à approximations successives

CAN algorithmiques

CAN flash

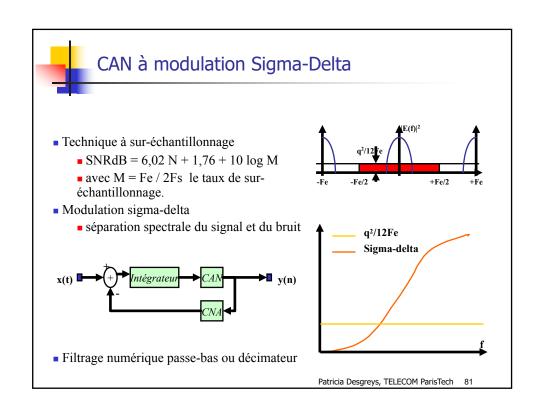

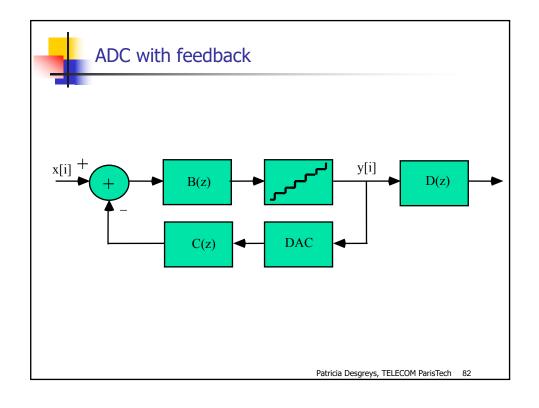

Technique du sur échantillonnage et conversion  $\Sigma\Delta$

**□ADC** performance: State-of-the-art

# 4

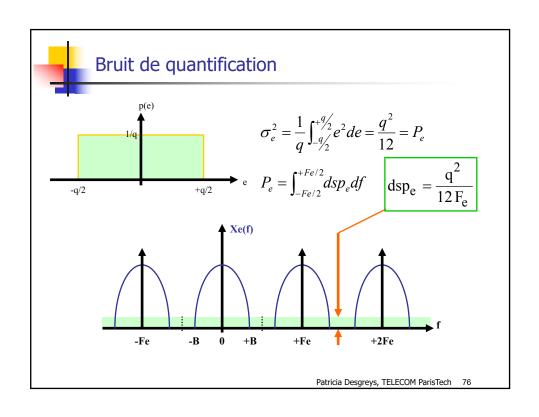

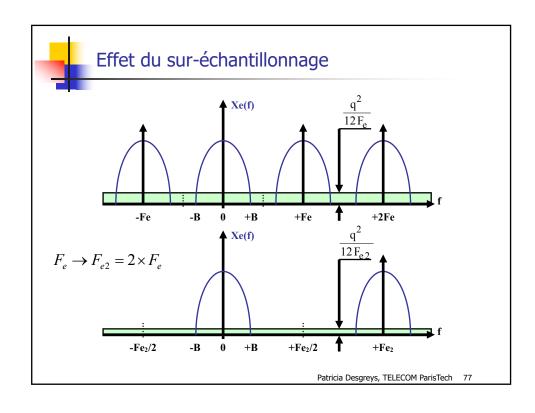

# Rapport signal/bruit (1)

Signal sinusoïdal :

$$x(t) = a \cdot \sin(2\pi f_s t)$$

$P_x = \frac{a^2}{2}$

$$P_{e\ bande\ utile} = \int_{-F_s}^{+F_s} ds p_e df = \frac{q^2}{12\,F_e} \cdot \underbrace{\widehat{^F_{Nyquist}}}_{F_{s}} = \frac{q^2}{12\,OSR}$$

$$q = \frac{2 \cdot a_0}{2^n - 1}$$

$$SNR = 10\log\left(\frac{P_x}{P_{eb.u.}}\right) = 10\log\frac{3}{2} + 20\log\frac{a}{a_0} + 20\log(2^n - 1) + 10\log OSR$$

# Rapport signal/bruit (2)

Hypothèses :  $a = a_0$   $OSR = 2^L$   $ntel\ que\ 2^n >> 1$

$$SNR_{(dB)} = 10 \log \left( \frac{P_x}{P_{eb.u.}} \right) \approx 1,76 + 6,02 \cdot n + 3,01 \cdot L$$

Il faut quadrupler la fréquence d'échantillonnage pour gagner l'équivalent d'un bit de quantification.

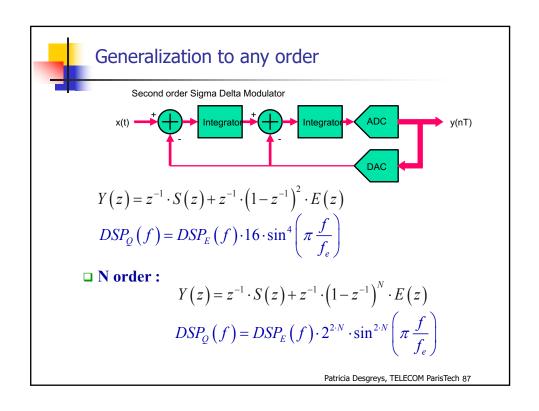

### Signal Noise Ratio of the ΣΔ modulator

$$SNR = \frac{P_{signal}}{P_{bruit}} \longrightarrow P_{gignal} = \frac{S_{max}^{2}}{2} \qquad OSR = \frac{fe}{2f_{S}} = 2^{L}$$

$$SNR = \frac{P_{signal}}{P_{bruit}} \longrightarrow P_{Q} = \frac{\Delta^{2}}{12} \cdot \frac{\pi^{2 \cdot N}}{2 \cdot N + 1} \cdot OSR^{-(2 \cdot N + 1)}$$

$$SNR = SNR_{quantiser} + \Delta SNR \qquad \Delta = \frac{2 \cdot ref}{2^{n} - 1}$$

$$\Delta SNR = 10 \cdot \log(2 \cdot N + 1) - N \cdot 20 \cdot \log \pi + L \cdot N \cdot 20 \cdot \log 2$$

$$SNR_{quantiser} = 10 \cdot \log \frac{3}{2} + 20 \cdot \log \frac{S_{max}}{ref} + 20 \cdot \log(2^{n} - 1) + L \cdot 10 \cdot \log 2$$

Patricia Desgreys, TELECOM ParisTech 89

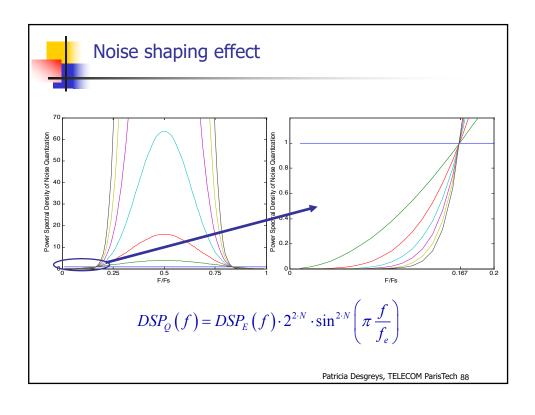

## Quantization noise and oversampling effects

- **□** Only oversampling effect

- $\square$  N=0; L=log|2OSR

- +3.01dB/octave of Fs

- ☐ Oversampling and Noise Shaping effects

- □ *N*=1

- +9.03dB/octave of Fs

- □ *N*=2

- +15.05dB/octave of Fs

- □ *N*=3

- +21.07dB/octave of Fs

- □ *N*=4

- +27.09dB/octave of Fs

Smax = ref, n = 1

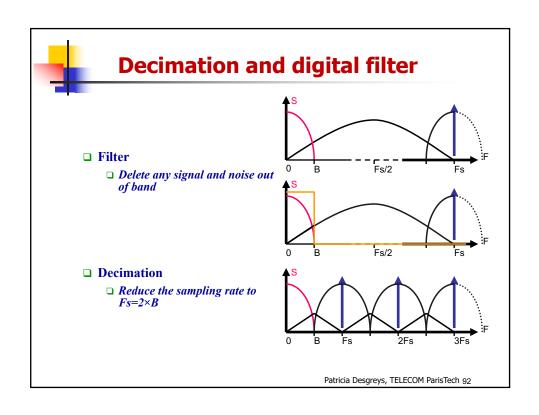

+ Filtrage analogique passe-bas de y(t)

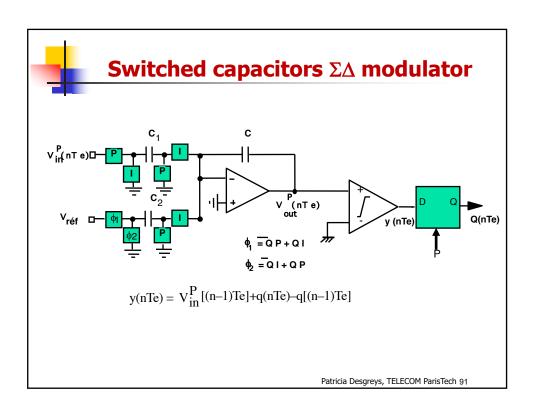

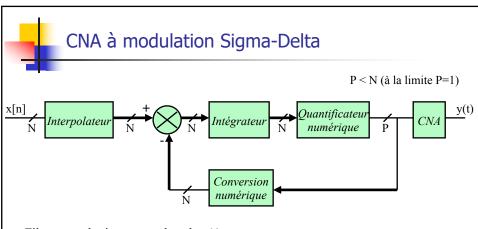

Les convertisseurs Sigma-Delta sont une alternative attractive pour la haute résolution (16 bits). Ils pallient la perte de précision inhérente aux circuits analogiques réalisés en technologies numériques grâce à un traitement du signal plus rapide et à plus de circuits numériques. Donc, ils capitalisent la vitesse des circuits analogiques et la précision des circuits numériques.

Inconvénient : le sur échantillonnage limite la bande du signal d'entrée (qq. MHz)

Patricia Desgreys, TELECOM ParisTech 93

# La conversion analogique numérique

Définition

Échantillonnage blocage

CAN à approximations successives

CAN algorithmiques

CAN flash

Technique du sur échantillonnage et conversion  $\Sigma\Delta$

**□ADC** performance: State-of-the-art

### Performance parameters

#### ■ Speed :

- Speed : Nyquist sampling rate :  $F_N$   $F_N = 2BW$  • Bandwidth : BW  $OSR = \frac{F_s}{2BW}$

### ■ Accuracy:

- · Stated resolution : N

- Signal to Noise and Distortion Ratio : SNDR  $ENOB = \frac{SNDR 1.76}{6.02}$  Effective number of bits : ENOB

- · Effective number of bits : ENOB

- · Spurious Free Dynamic Range: SFDR

#### ■ Power :

- Power consumption :  $P_{\text{diss}}$

- · Figure of Merit : FoM

$$FoM = \frac{P_{diss}}{2^{ENOB} \cdot 2BW} \quad [pJ/step]$$

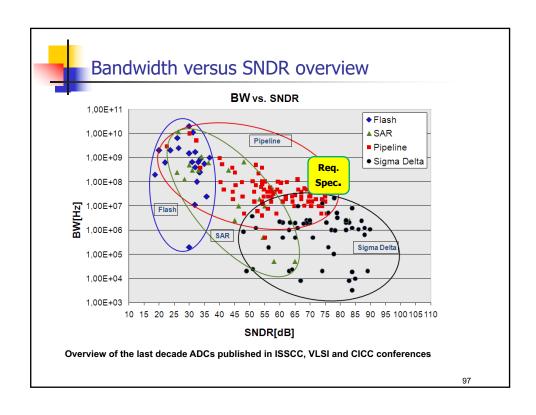

# Required specifications on the ADC

Analog-to-digital converters are key blocks in modern communication systems.

- 70 to 80 dB of SNR

- · more than 50dB of SFDR

- 100 MHz -1 GHz of Bandwidth

- 0.1 pJ by conversion step

# Conclusion: Promising Techniques

- For future 5G radio requirements :

- ΔΣ converters and CT implementations

- Pipeline converters

- Parallel implementation and increasing use of calibration and digital correction

- For multi-channel cable receiver :

- TI SAR converters

- An attractive solution:

- CT BP  $\Delta\Sigma$  converters and Parallelism

98