Institut Mines-Telecom

# Digital CMOS Low Power Design

Chadi Jabbour

Electronics for embedded systems

#### **Outline**

Why low power in embedded systems?

Power consumption in CMOS, what is it?

Reducing Dynamic power

Reducing static and leakage power

Conclusion and methodology

#### Outline

#### Why low power in embedded systems?

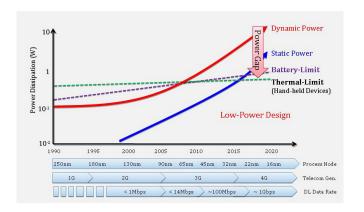

### Why low power-1

Battery life is not evolving as fast as silicon technologies!!!

## Why low power-2

## Why low power-3

Power results in Heat  $\Longrightarrow$  we need cooling  $\Longrightarrow$  more power

#### **Outline**

Why low power in embedded systems?

Power consumption in CMOS, what is it?

Reducing Dynamic power

Reducing static and leakage power

Conclusion and methodology

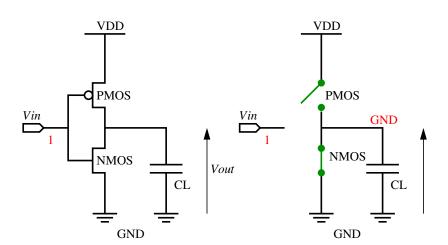

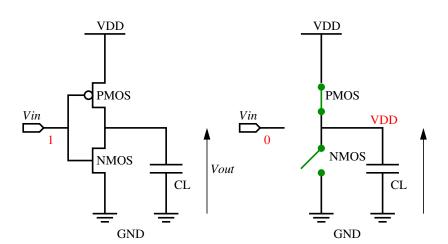

## **Example**

## **Example**

## **Example**

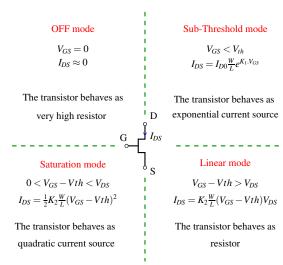

#### **CMOS** Transistors state - reminder NMOS

$V_{th}$ : Threshold Voltage - - - W: transistor width - - - L transistor length  $I_{D0}$ ,  $K_1$  and  $K_2$  are constants that depend on the technology and the transistor type

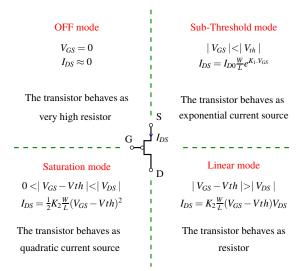

#### **CMOS Transistors state - reminder PMOS**

The behavior of a PMOS is similar to an NMOS except that  $V_{GS}$ ,  $V_{DS}$  &  $V_{th}$  < 0  $I_{D0}$ ,  $V_{th}$ ,  $K_1$  and  $K_2$  are not equal for PMOS and NMOS

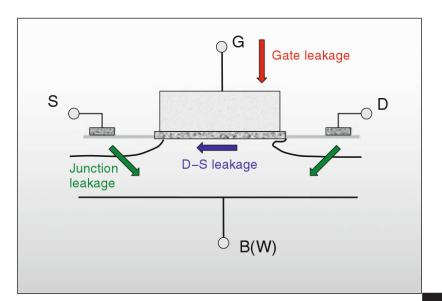

## **Leakage Current**

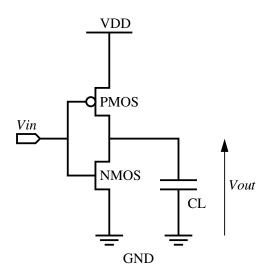

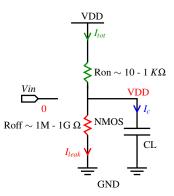

### Power consumption calculation

- 1-Assuming  $Roff \infty$ , what is the energy needed to charge CL to VDD?

- 2-If Vin is a signal of frequency freq and a probability of toggling  $\alpha$ , what will be the power consumption of our circuit?

## Power consumption overall

$$P = \underbrace{\frac{1}{2} \cdot \alpha \cdot CL \cdot freq \cdot VDD^2}_{Dynamic\ Power} + \underbrace{I_{leak} \cdot VDD}_{Leakage\ Power}$$

$\alpha$  is the activity or the probability to have a toggle in the gate CL is the load freq is the operation frequency VDD is the power supply  $I_{leak}$  is the leakage current

### **Outline**

Why low power in embedded systems?

Power consumption in CMOS, what is it?

Reducing Dynamic power

Reducing static and leakage power

Conclusion and methodology

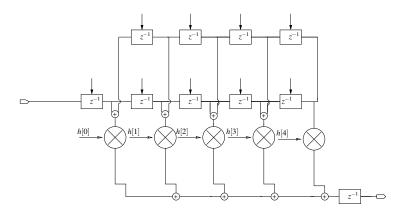

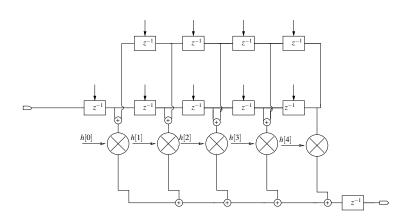

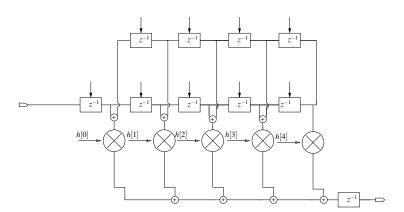

## Reduce the number of devices -Symmetry

if

$$h[0] = h[8]$$

,  $h[1] = h[7]$ ,  $h[2] = h[6]$ ,  $h[3] = h[5]$

N/2 instead of N multipliers

## Reduce the number of devices - Half band filters

Half of the coefficients are equal to zero

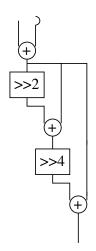

## Reduce the number of devices - Multiplierless filters

## Reduce the number of devices - Multiplierless filters

$$h[0] = 81 = 1 \times 2^6 + 0 \times 2^5 + 1 \times 2^4 + 0 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$$

## Reduce the number of devices - Multiplierless filters

$$h[0] = 81 = 1 \times 2^6 + 0 \times 2^5 + 1 \times 2^4 + 0 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$$

## Power consumption overall

$$P = \underbrace{\frac{1}{2} \cdot \alpha \cdot CL \cdot freq \cdot VDD^2}_{Dynamic\ Power} + \underbrace{I_{leak} \cdot VDD}_{Leakage\ Power}$$

$\alpha$  is the activity or the probability to have a toggle in the gate CL is the load freq is the operation frequency VDD is the power supply  $I_{leak}$  is the leakage current

CL = Transistor capacitances + Interconnect capacitances

CL = Transistor capacitances + Interconnect capacitances

CL = Transistor capacitances + Interconnect capacitances

- ► The transistor capacitances are proportional to *W.L* of the connected transistors

- ► The interconnect capacitances depend on the length and width of the wire.

CL = Transistor capacitances + Interconnect capacitances

- ► The transistor capacitances are proportional to *W.L* of the connected transistors

- ► The interconnect capacitances depend on the length and width of the wire.

Hence, reducing  $\it CL$  can be done by using a smaller technology node (65 nm instead 130 nm, or 28 nm instead of 90 nm) but smaller technologies are:

- ► More expensive

- ▶ (often) more leaky

## Power consumption overall

$$P = \underbrace{\frac{1}{2} \cdot \alpha \cdot CL \cdot freq \cdot VDD^2}_{Dynamic\ Power} + \underbrace{I_{leak} \cdot VDD}_{Leakage\ Power}$$

$\alpha$  is the activity or the probability to have a toggle in the gate CL is the load freq is the operation frequency VDD is the power supply  $I_{leak}$  is the leakage current

### How to reduce $\alpha$ -encoding

Encoding consists in changing the representation of the information in a manner that reduces the average number of transitions.

Example: Grey Encoding

| Binary                       |                | Gray-code                 |                |

|------------------------------|----------------|---------------------------|----------------|

| State                        | No. of toggles | State                     | No. of toggles |

| 000                          | -              | 000                       | -              |

| 001                          | 1              | 001                       | 1              |

| 010                          | 2              | 011                       | 1              |

| 011                          | 1              | 010                       | 1              |

| 100                          | 3              | 110                       | 1              |

| 101                          | 1              | 111                       | 1              |

| 110                          | 2              | 101                       | 1              |

| 111                          | 1              | 100                       | 1              |

| 000                          | 3              | 000                       | 1              |

| Av. Transitions/clock = 1.75 |                | Av. Transitions/clock = 1 |                |

## How to reduce $\alpha$ -encoding

Example 2: Canonical Signed Digit (CSD)  $1010011111111 \Rightarrow 10101000000(-1)$

| number | 2's complement | CSD              |

|--------|----------------|------------------|

| 3      | 011            | $10\overline{1}$ |

| 2      | 011            | 010              |

| 1      | 001            | 001              |

| 0      | 000            | 000              |

| -1     | 111            | 001              |

| -2     | 110            | 010              |

| -3     | 101            | <u>1</u> 01      |

| -4     | 100            | <u>1</u> 00      |

33% of non zero bits for CSD with respect to 50% for classical encoding

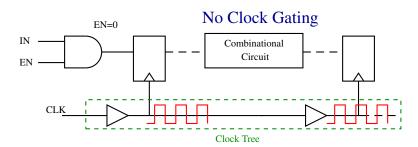

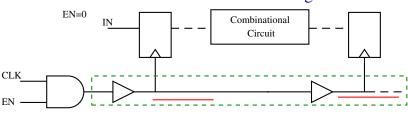

## How to reduce $\alpha$ -Clock Gating

## With Clock Gating

Clock Tree

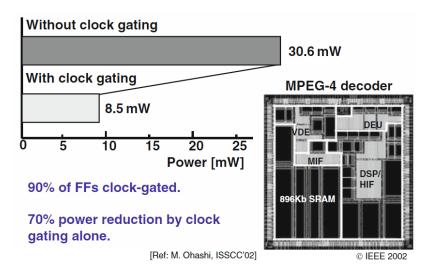

## How to reduce $\alpha$ -Clock Gating Application

## Power consumption overall

$$P = \underbrace{\frac{1}{2} \cdot \alpha \cdot CL \cdot freq \cdot VDD^2}_{Dynamic\ Power} + \underbrace{I_{leak} \cdot VDD}_{Leakage\ Power}$$

$\alpha$  is the activity or the probability to have a toggle in the gate CL is the load freq is the operation frequency VDD is the power supply  $I_{leak}$  is the leakage current

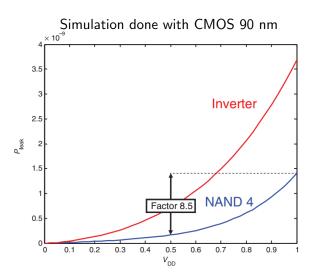

## Reduce VDD - Impact

Reducing VDD has an impact of the delay of the gates

$$delay \propto rac{VDD}{(VDD-V_{th})^K}$$

- K is a variable that depends on many parameters such as the technology, VDD, V<sub>th</sub>.

- ▶ Its value is typically between 1.5 and 2.

Reducing VDD increases the delay and therefore the systems should be adapted to keep the same performance

## Reduce VDD - Impact

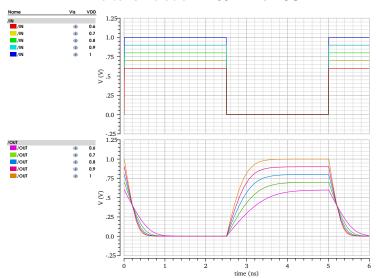

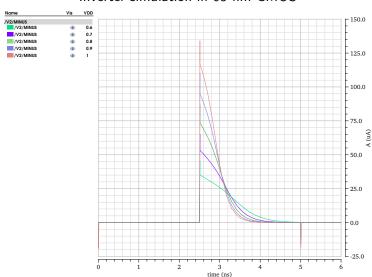

#### Inverter simulation in 65 nm CMOS

## Reduce VDD - Impact

#### Inverter simulation in 65 nm CMOS

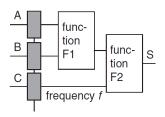

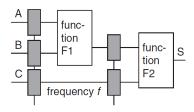

## How to reduce VDD - pipelining

#### Basic circuit

#### Pipelined circuit

Pipelining allows to reduce the length of the critical path and thus to reduce VDD

But it increases the delay between the input and the output and it requires additional material (Flip-Flops)

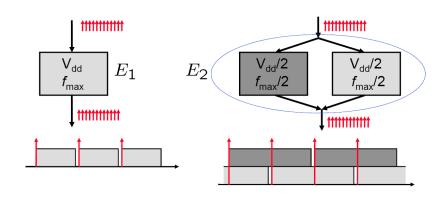

## How to reduce the VDD-Parallelizing

Parallelism allows to reduce the frequency per channel/path thus to reduce VDD

The circuit is duplicated  $\implies$  higher area, higher leakage (Maybe)

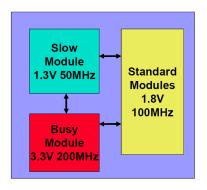

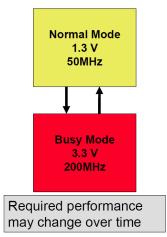

## Multiple and Dynamic VDD

Not all components require same performance.

Using multiple and Dynamic VDD reduces the power consumption It increases the complexity of the power generation block

### **Outline**

Why low power in embedded systems?

Power consumption in CMOS, what is it?

Reducing Dynamic power

Reducing static and leakage power

Conclusion and methodology

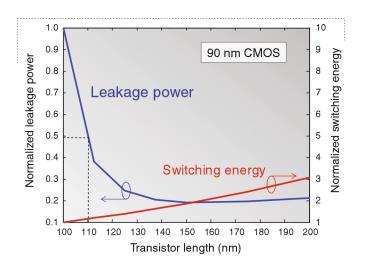

#### How to reduce $I_{leak}$ - Use wider transitor

The higher the L, the lower the leakage current but the slower the transistors

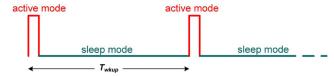

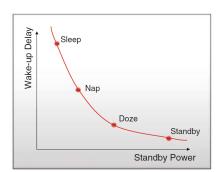

#### Fais dodo?

For low speed applications such as sensors, the system can be sent to sleep (Nap/Doze) to minimize leakage:

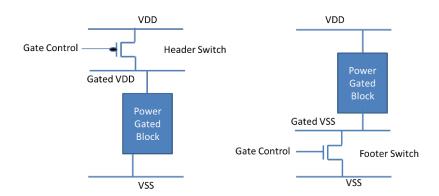

## How to reduce $I_{leak}$ - Power gating

- Power gating can be done either on VDD or the ground

- ▶ The switch is implemented using a high  $V_{th}$  transistor with a high length in order to reduce the leakage

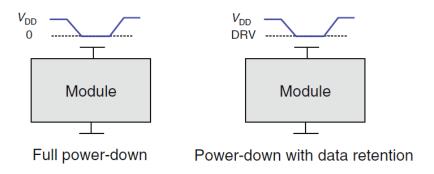

# How to reduce $I_{leak}$ - Supply voltage Ramping

- ► Supply voltage ramping is the most efficient approach to reduce leakage but it requires a controllable voltage regulator

- ► The supply voltage can be reduced down to "0" if no data retention is needed.

# How to reduce $I_{leak}$ - Supply voltage Ramping

### **Outline**

Why low power in embedded systems?

Power consumption in CMOS, what is it?

Reducing Dynamic power

Reducing static and leakage power

Conclusion and methodology

#### Conclusion

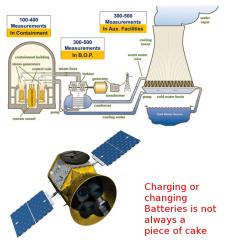

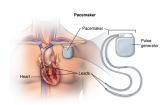

- Minimizing power consumption is very important in embedded systems in order to

- Save energy and ecological reasons

- Reduce cost of changing or charging batteries difficult to access (Human body, satellites, agriculture, ...)

- Avoiding heating the system

- Dynamic Power consumption can be minimized by:

- Capacitor: Smaller technologies, better layout, slower speed

- ▶ \ Activity: Clock Gating, glitches suppression, encoding, ...

- ▶ \ Vdd (dynamic): Pipelining and parallelism, ...

- Static or leakage power consumption can be minimized by:

- $ightharpoonup

ightharpoonup I_{leak}$ : Multiple  $V_{th}$ , use lower VDD, ...

- ▶ \ VDD (static): Power gating, Supply voltage ramping, ...

#### References

A. P. Chandrakasan et al., "Low-power cmos digital design," IEEE JSSC, vol. 27, no. 4, pp. 473-484, Apr 1992.

J. T. Kao et al., "A 175-mv multiply-accumulate unit using an adaptive supply voltage and body bias architecture," IEEE Journal of Solid-State Circuits, vol. 37. no. 11. pp. 1545-1554. Nov 2002.

K. Roy et al., "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits," Proceedings of the IEEE, vol. 91, no. 2, pp. 305-327. Feb 2003.

J. Rabaev. Low Power Design Essentials. Springer, 2009.

P. Ranjan et al., Power-efficient System Design. Boston, MA: Springer US. 2010, ch. Basic Low Power Digital Design, pp. 11–39.

M. Slimani, "Low energy design of digital circuits," Ph.D. dissertation, Telecom Paristech, 2012.

M. Alioto, "Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial," *IEEE TCAS I*, vol. 59, no. 1, pp. 3–29, Jan 2012.

T. Austin, "On the rules of low power design," 2013. [Online]. Available: https://www.youtube.com/watch?v=jpkiFRRX1g8

A. Pal, "Low power vlsi circuits and systems," 2015. [Online]. Available: https://www.youtube.com/watch?v=bKhs2Wv3Kb4

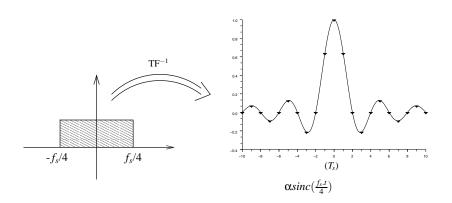

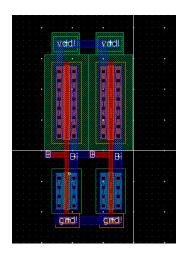

# Methodology - Design example: Decimation filter

► Application level :

Architecture and system level :

► Gate and circuit level :

# Methodology - Design example: Decimation filter

- Application level :

- Is there anyway to relax my specifications?

- ► Should my system be ON all the time?

- ▶ ...

- Architecture and system level :

- ▶ What is the best architecture for my system?

- ▶ Should i do the decimation in 1 step, 2 steps ...?

- How many coefficients for each of my filters?

- On how many bits should i code my coefficients?

- Should i use any type of encoding?

- · ...

- Gate and circuit level :

- ► Technology, gate sizing

- ► Pipelining, parallelism

- ▶ Multiple V<sub>th</sub>, Lower VDD, multiple VDD

- Design custom gates to improve power

- **.**.